C1.2

Debug access

The processor implements the Armv8 Debug architecture and debug events. Accessing system registers

allows the processor to access certain debug registers directly. The external debug interface enables both

external and self-hosted debug agents to access debug registers.

The partitioning of debug register access is as follows:

Debug registers

Access is based on the system registers and is memory-mapped. You can access the debug

register map using the APB slave port.

PMU

Access is based on the system registers and is memory-mapped. You can access the performance

monitor registers using the APB slave port.

ETM

Access is memory-mapped.

CTI

Access is based on the debug registers and is memory-mapped.

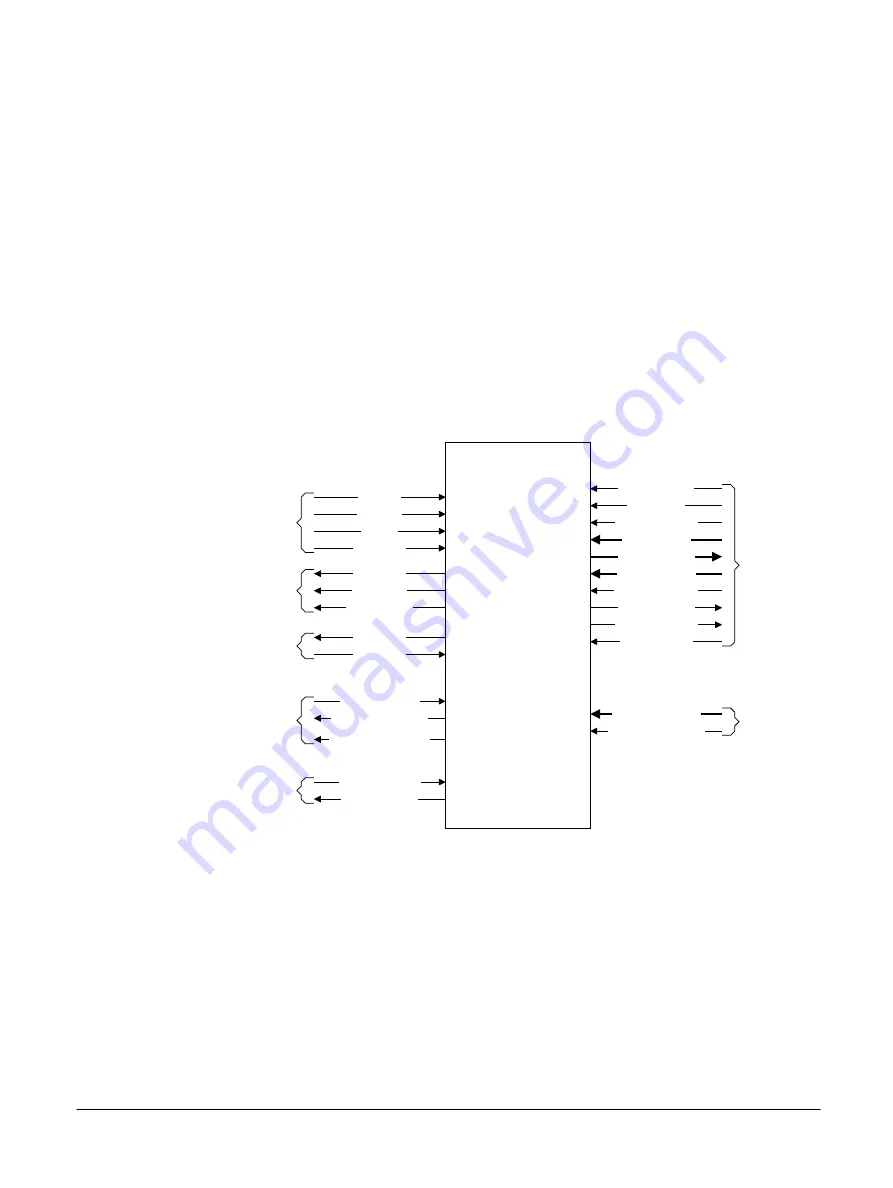

DBGEN

SPIDEN

NIDEN

SPNIDEN

Authentication

interface

COMMTX

COMMRX

DCC

handshake

DBGACK

EDBGRQ

DBGPWRDUP

Power

controller

interface

PSELDBG

PADDRDBG

PRDATADBG

PWDATADBG

PENABLEDBG

PREADYDBG

PSLVERRDBG

PWRITEDBG

PCLKENDBG

Debug slave

port, APBv3

Debug state

entry

DBGROMADDR

DBGROMADDRV

Processor

DBGRSTREQ

Reset

controller

interface

DBGPWRUPREQ

nCOMMIRQ

DBGNOPWRDWN

nPRESETDBG

Configuration

PADDRDBG31

Figure C1-2 External debug interface

Related information

Chapter C4 CTI

on page C4-603

Appendix A Signal Descriptions

C1 Debug

C1.2 Debug access

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C1-577

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......