C1.6

Debug memory map

The basic memory map supports up to four cores in the cluster. You can configure the mapping as a v8 or

as a v7 Debug memory map.

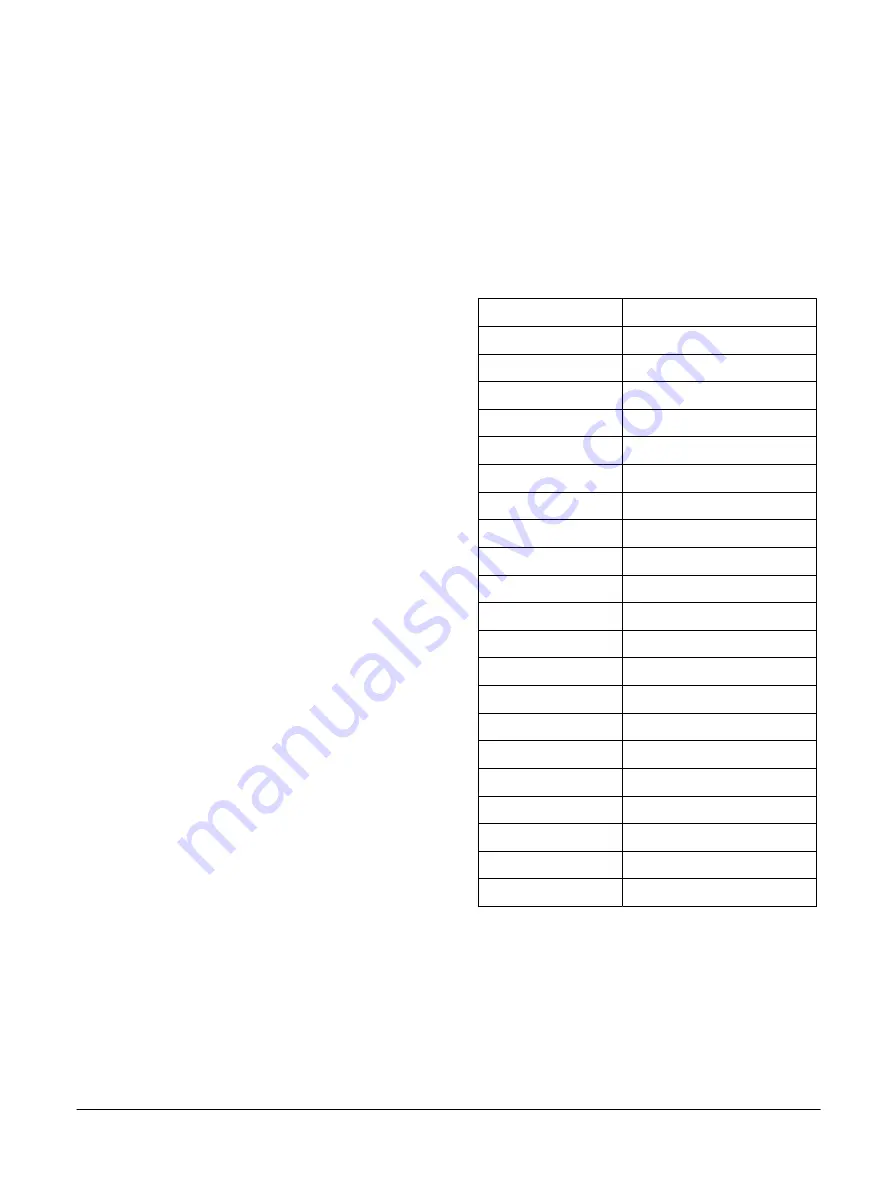

The following table shows the address mapping for the debug APB components when you configure

them for a v8 Debug memory map. Each component in the table requires 4KB and uses the bottom 4KB

of each 64KB region. The remaining 60KB of each region is reserved. The table indicates the mapped

component if it is present, otherwise the field is reserved.

Table C1-3 Address mapping for APB components in a v8 Debug memory map

Address offset [21:0] Mapped to

0x000000

-

0x000FFF

APB ROM table for the processor

0x010000

-

0x010FFF

Core 0 Debug

0x020000

-

0x020FFF

Core 0 CTI

0x030000

-

0x030FFF

Core 0 PMU

0x040000

-

0x040FFF

Core 0 Trace

0x041000

-

0x10FFFF

Reserved

0x110000

-

0x110FFF

Core 1 Debug

0x120000

-

0x120FFF

Core 1 CTI

0x130000

-

0x130FFF

Core 1 PMU

0x140000

-

0x140FFF

Core 1 Trace

0x141000

-

0x20FFFF

Reserved

0x210000

-

0x210FFF

Core 2 Debug

0x220000

-

0x220FFF

Core 2 CTI

0x230000

-

0x230FFF

Core 2 PMU

0x240000

-

0x240FFF

Core 2 Trace

0x241000

-

0x30FFFF

Reserved

0x310000

-

0x310FFF

Core 3 Debug

0x320000

-

0x320FFF

Core 3 CTI

0x330000

-

0x330FFF

Core 3 PMU

0x340000

-

0x340FFF

Core 3 Trace

0x341000

-

0x3FFFFF

Reserved

The following table shows the address mapping for the debug components when you configure them for

a v7 Debug memory map. The table indicates the mapped component if it is present, otherwise the field

is reserved.

C1 Debug

C1.6 Debug memory map

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C1-581

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......