C5.2

Encoding for tag and data in the L1 instruction cache

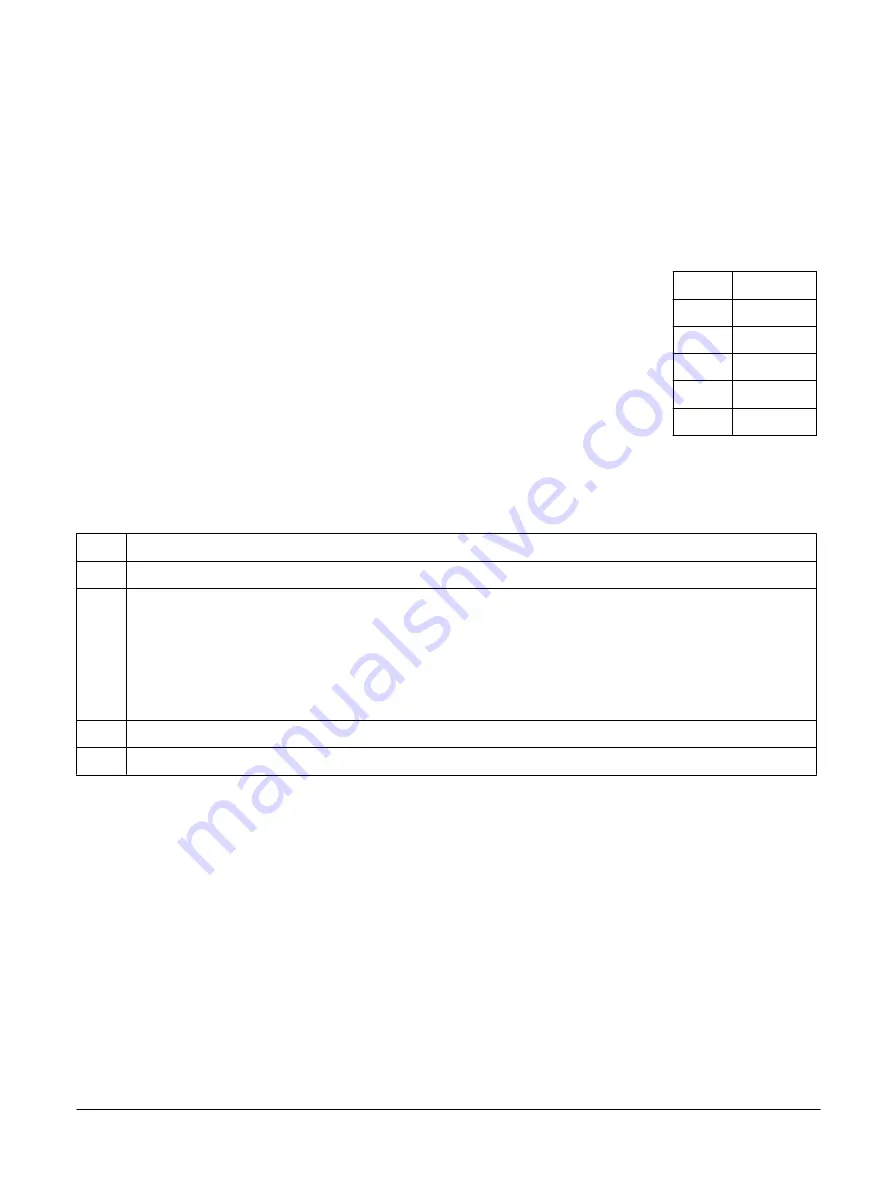

The following table shows the format of the Instruction Cache Tag Read Operation Register and the

Instruction Cache Data Read Operation Register.

The set-index range parameter (S) is determined by the following formula:

S = log

2

(size of the instruction cache in bytes / 2)

Table C5-3 Instruction cache tag and data location encoding

Bit field Description

[31]

Cache Way

[30:S]

Unused

[S-1:6]

Set index

[5:2]

Line offset

[1:0]

Unused

The following table shows the format of the information in Data Register 0 following an Instruction

Cache Tag Read Operation.

Table C5-4 Instruction cache tag data format

Bits

Description

[31]

Unused.

[30:29] Valid and set mode:

0b00

A32.

0b01

T32.

0b10

A64.

0b11

Invalid.

[28]

Non-secure state (NS).

[27:0]

Tag address.

The Instruction Cache Data Read Operation returns two entries from the cache in Data Register 0 and

Data Register 1 corresponding to the 16-bit aligned offset in the cache line:

Data Register 0

Bits[19:0] data from cache

0b00

.

Data Register 1

Bits[19:0] data from cache

0b10

.

In A32 or A64 state these two fields combined always represent a single predecoded instruction. In T32

state, they can represent any combination of 16-bit and partial or full 32-bit instructions.

C5 Direct access to internal memory

C5.2 Encoding for tag and data in the L1 instruction cache

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C5-609

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......