A4.2

Power modes

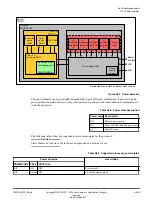

The processor supports the following power modes:

Normal mode

This is the normal mode of operation in which all of the processor functionality is available. The

Cortex

‑

A35 processor uses gated clocks to disable inputs to unused functional blocks. Only the

logic used to perform an operation consumes any dynamic power.

Standby mode

When a Cortex

‑

A35 core is in standby mode, it is architecturally clock gated at the top of the

clock tree. Each core in the cluster can be put in standby mode separately from the other cores,

by executing a

Wait for Interrupt

(WFI) or

Wait for Event

(WFE) instruction.

L2 standby mode

When all the cores are in standby mode and the L2 memory system is idle.

Individual core shutdown mode

The PDCPU power domain for an individual core is shut down and the state held in this domain

is lost.

Cluster shutdown mode

The PDMERCURY, PDL2, and all PDCPU power domains are shut down and the state held in

these domains is lost.

Dormant mode (optional)

All the cores and L2 control logic are powered down while the L2 cache RAMs are powered up

and retain state. The RAM blocks that remain powered up during Dormant mode are:

• L2 tag RAMs.

• L2 data RAMs.

• L2 victim RAM.

Retention mode

Contact Arm for information about retention state.

A4 Power Management

A4.2 Power modes

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A4-61

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......