C10.7

Performance Monitors Common Event Identification Register 0, EL0

The PMCEID0_EL0 characteristics are:

Purpose

Defines which common architectural and common microarchitectural feature events are

implemented.

Usage constraints

This register is accessible as follows:

EL0

EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

Config RO

RO

RO

RO

RO

This register is accessible at EL0 when PMUSERENR_EL0.EN is set to 1.

Configurations

The PMCEID0_EL0 is architecturally mapped to:

• The AArch32 register PMCEID0. See

C10.3 Performance Monitors Common Event

.

• The external register PMCEID0_EL0.

Attributes

PMCEID0_EL0 is a 32-bit register.

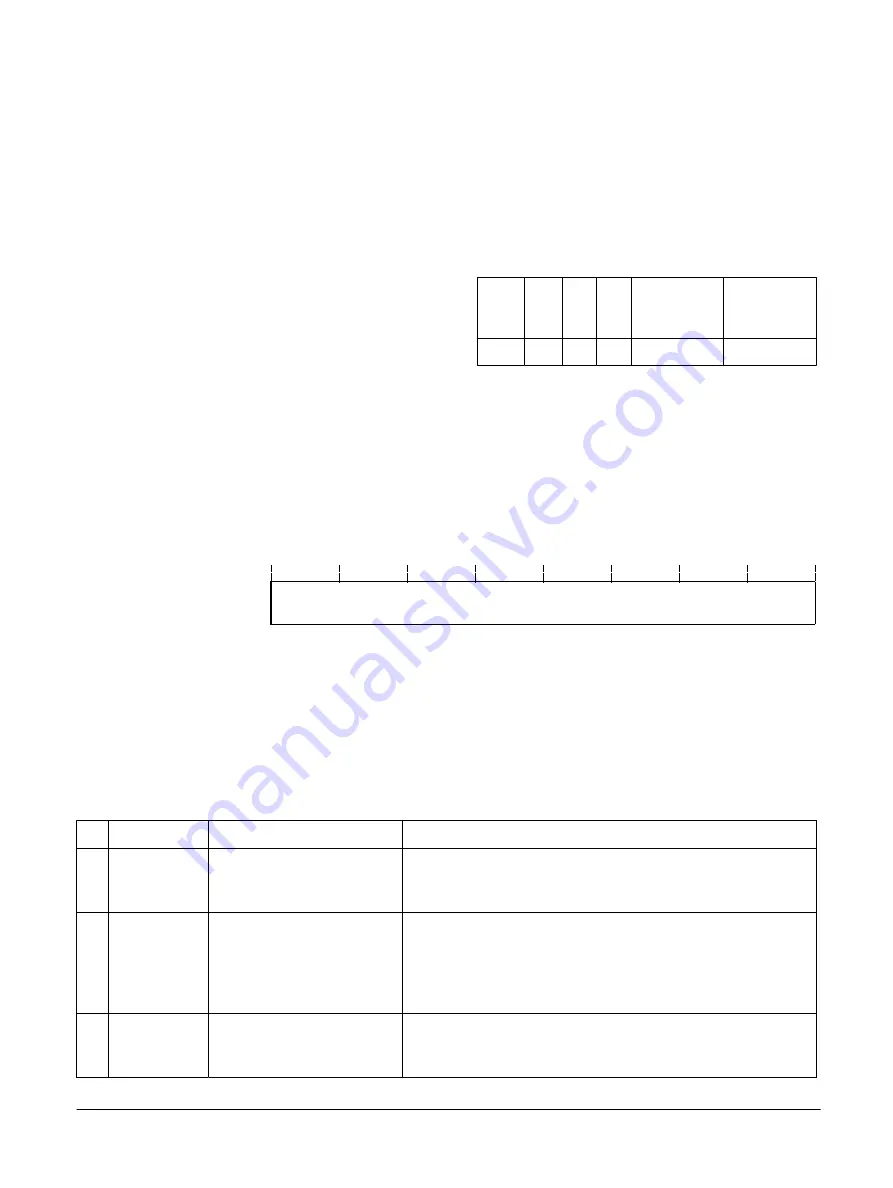

CE

31

0

8 7

16 15

1

2

3

4

6

11

12

30 29 28 27 26 25 24 23 22 21 20 19 18 17

13

14

9

10

5

Figure C10-5 PMCEID0_EL0 bit assignments

CE[31:0], [31:0]

Common architectural and microarchitectural feature events that can be counted by the PMU

event counters.

For each bit described in the following table, the event is implemented if the bit is set to 1, or

not implemented if the bit is set to 0.

Table C10-5 PMU common events

Bit Event number Event mnemonic

Description

[31]

0x1F

L1D_CACHE_ALLOCATE

L1 Data cache allocate:

0

This event is not implemented.

[30]

0x1E

CHAIN

Chain. For odd-numbered counters, counts once for each overflow of the

preceding even-numbered counter. For even-numbered counters, does not

count:

1

This event is implemented.

[29]

0x1D

BUS_CYCLES

Bus cycle:

1

This event is implemented.

C10 PMU registers

C10.7 Performance Monitors Common Event Identification Register 0, EL0

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C10-707

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......