C11.9

Stall Control Register

The TRCSTALLCTLR characteristics are:

Purpose

Enables the ETM trace unit to stall the Cortex

‑

A35 processor if the ETM trace unit FIFO

overflows.

Usage constraints

• You must always program this register as part of trace unit initialization.

• Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See

RES

0

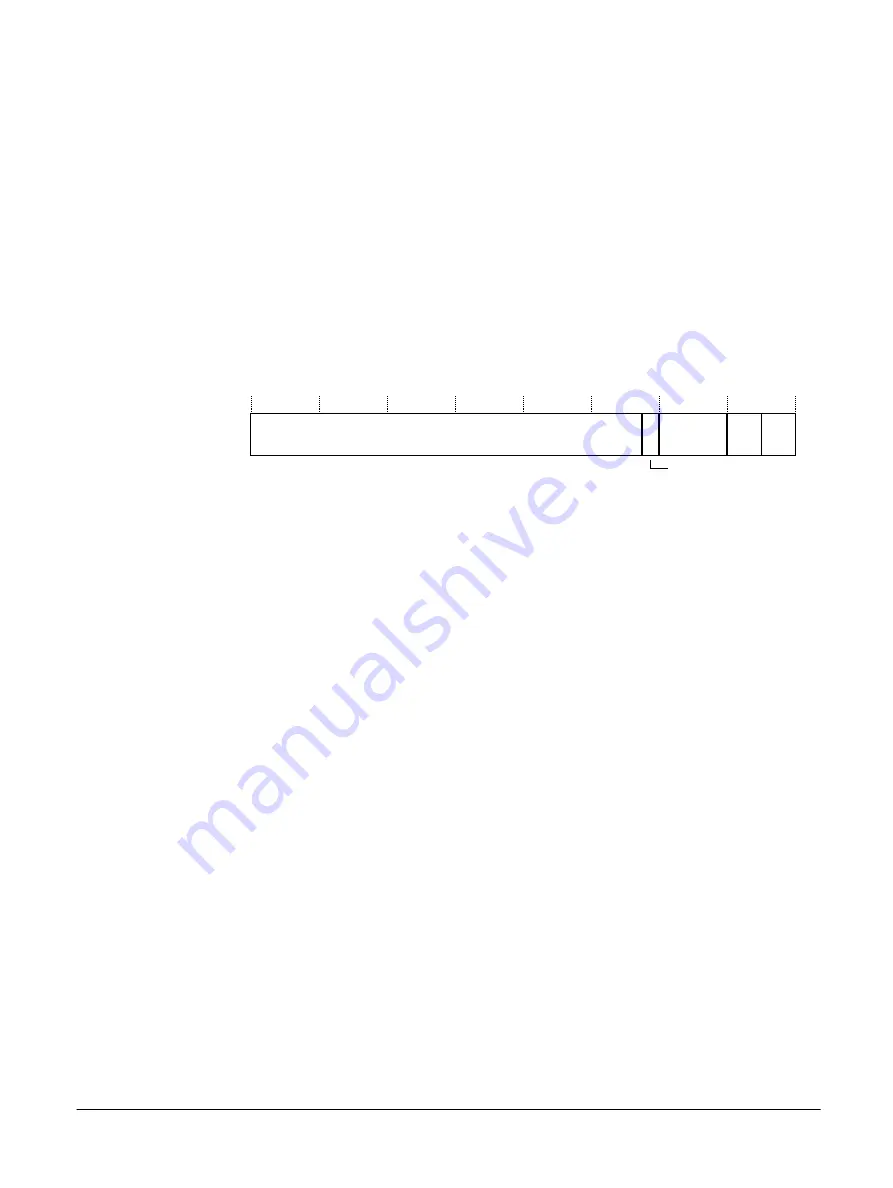

31

0

7

4

RES

0

3

ISTALL

8

9

LEVEL

RES

0

2 1

Figure C11-8 TRCSTALLCTLR bit assignments

[31:9]

Reserved,

RES0

.

ISTALL, [8]

Instruction stall bit. Controls if the trace unit can stall the processor when the instruction trace

buffer space is less than LEVEL:

0

The trace unit does not stall the processor.

1

The trace unit can stall the processor.

[7:4]

Reserved,

RES0

.

LEVEL, [3:2]

Threshold level field. The field can support 4 monotonic levels from

0b00

to

0b11

, where:

0b00

Zero invasion. This setting has a greater risk of an ETM trace unit FIFO overflow.

0b11

Maximum invasion occurs but there is less risk of a FIFO overflow.

[1:0]

Reserved,

RES0

.

The TRCSTALLCTLR can be accessed through the external debug interface, offset

0x02c

.

C11 ETM registers

C11.9 Stall Control Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-746

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......