A4.16

STANDBYWFI[3:0] and STANDBYWFIL2 signals

The

STANDBYWFI[n]

signal indicates when an individual core is in idle and low-power state. The

power management controller can remove power from an individual core when

STANDBYWFI[n]

is

asserted.

The

STANDBYWFIL2

signal indicates when all individual cores and the L2 memory system are in idle

and low-power state. A power management controller can remove power from the Cortex

‑

A35 processor

when

STANDBYWFIL2

is asserted. See

A4.8 Powering down the processor without system driven L2

A4.10 Powering down the processor with system driven L2 flush

for more information.

The Cortex

‑

A35 processor includes a minimal L2 memory system in configurations without an L2 cache.

Therefore, the power management controller must always wait for assertion of

STANDBYWFIL2

before removing power from the Cortex

‑

A35 processor. This applies to configurations that use the mini-

SCU and configurations that use the SCU.

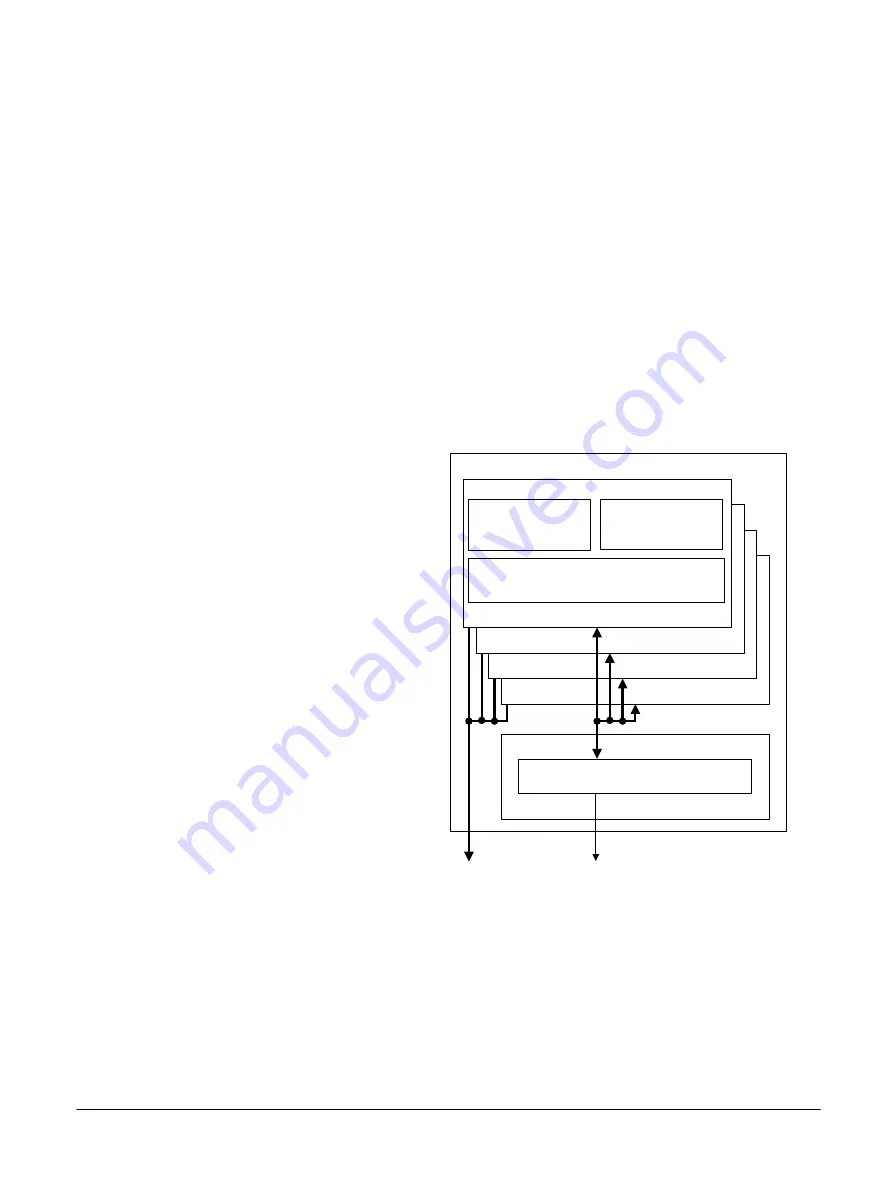

The following figure shows how

STANDBYWFI[3:0]

and

STANDBYWFIL2

correspond to individual

cores and the Cortex

‑

A35 processor.

Processor

Core 3

Level 2 memory system

Snoop Control Unit (SCU)

STANDBYWFI[3:0]

STANDBYWFIL2

Core 2

Core 1

Core 0

Level 1 memory system

Data Processing

Unit (DPU)

Instruction Fetch

Unit (IFU)

Figure A4-4 STANDBYWFI[3:0] and STANDBYWFIL2 signals

A4 Power Management

A4.16 STANDBYWFI[3:0] and STANDBYWFIL2 signals

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

A4-75

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......