C11.20 External Input Select Register

The TRCEXTINSELR characteristics are:

Purpose

Controls the selectors that choose an external input as a resource in the ETM trace unit. You can

use the Resource Selectors to access these external input resources.

Usage constraints

Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See

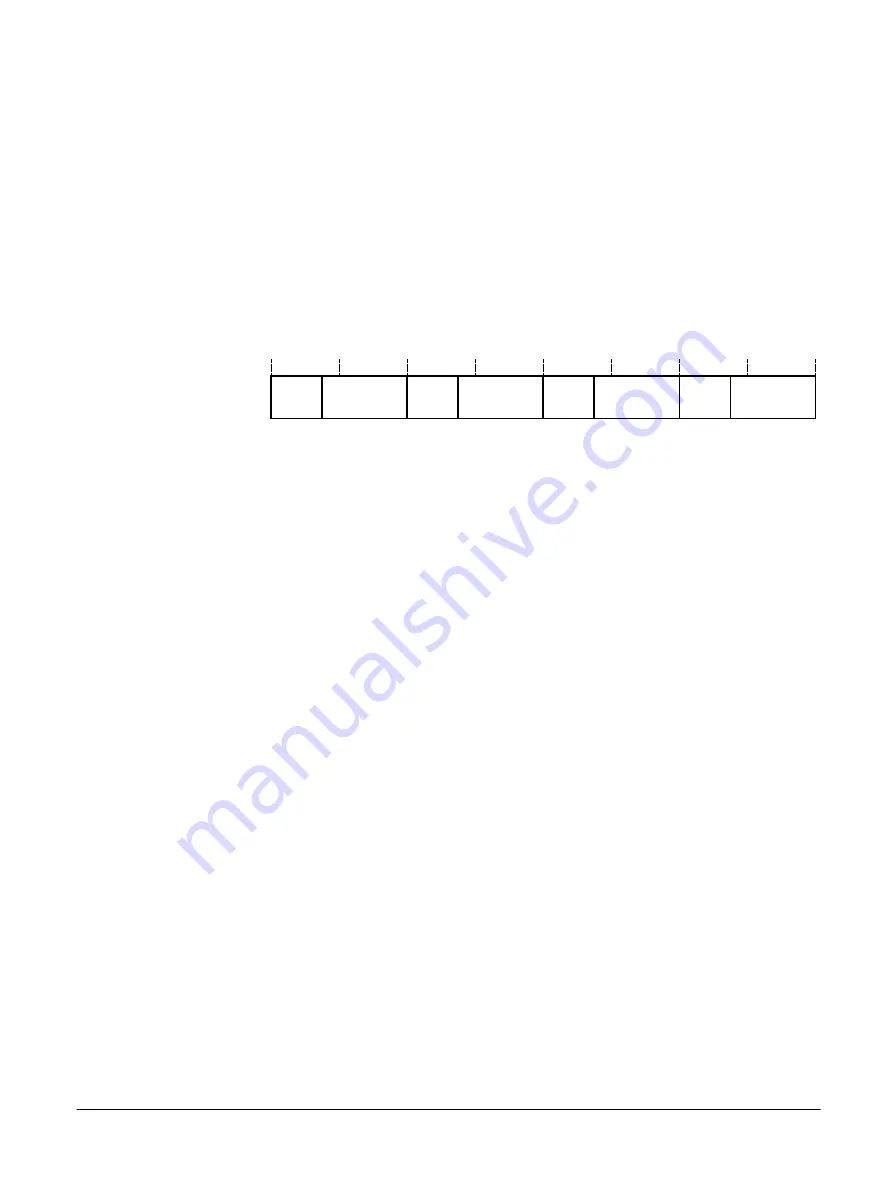

31

0

8 7

16 15

24 23

SEL2

SEL1

SEL0

SEL3

28

29

RES

0

RES

0

20

21

RES

0

12

13

RES

0

4

5

Figure C11-19 TRCEXTINSELR bit assignments

[31:29]

Reserved,

RES0

.

SEL3, [28:24]

Selects an event from the external input bus for External Input Resource 3.

[23:21]

Reserved,

RES0

.

SEL2, [20:16]

Selects an event from the external input bus for External Input Resource 2.

[15:13]

Reserved,

RES0

.

SEL1, [12:8]

Selects an event from the external input bus for External Input Resource 1.

[7:5]

Reserved,

RES0

.

SEL0, [4:0]

Selects an event from the external input bus for External Input Resource 0.

The TRCEXTINSELR can be accessed through the external debug interface, offset

0x120

.

C11 ETM registers

C11.20 External Input Select Register

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C11-759

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......