C12.1

Cross trigger register summary

This section describes the cross trigger registers in the Cortex

‑

A35 processor. These registers are

accessed through the external debug interface.

The following table gives a summary of the Cortex

‑

A35 cross trigger registers. For those registers not

described in this chapter, see the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture

profile

.

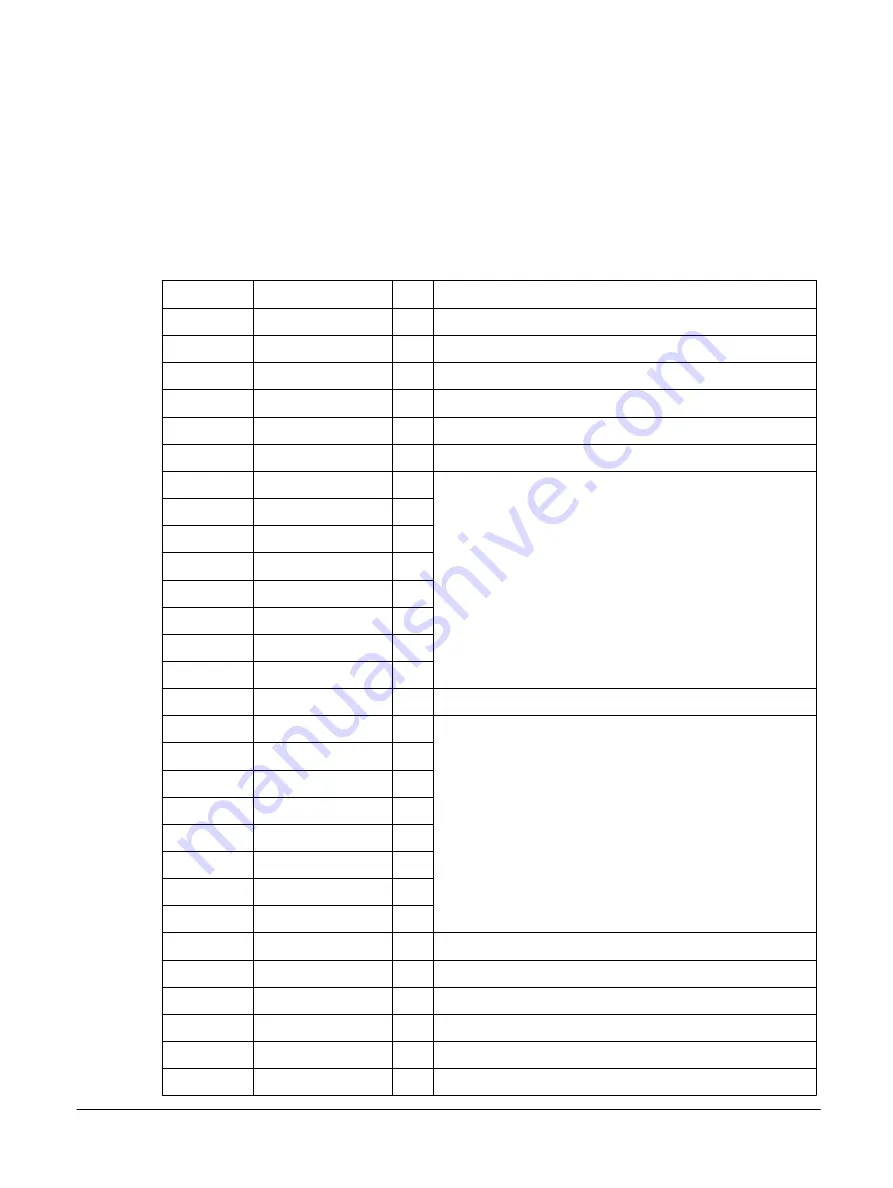

Table C12-1 Cross trigger register summary

Offset

Name

Type Description

0x000

CTICONTROL

RW

CTI Control Register

0x000-0x00C

-

-

Reserved

0x010

CTIINTACK

WO

CTI Output Trigger Acknowledge Register

0x014

CTIAPPSET

RW

CTI Application Trigger Set Register

0x018

CTIAPPCLEAR

WO

CTI Application Trigger Clear Register

0x01C

CTIAPPPULSE

WO

CTI Application Pulse Register

0x020

CTIINEN0

RW

CTI Input Trigger to Output Channel Enable Registers

0x024

CTIINEN1

RW

0x028

CTIINEN2

RW

0x02C

CTIINEN3

RW

0x030

CTIINEN4

RW

0x034

CTIINEN5

RW

0x038

CTIINEN6

RW

0x03C

CTIINEN7

RW

0x040-0x09C

-

-

Reserved

0x0A0

CTIOUTEN0

RW

CTI Input Channel to Output Trigger Enable Registers

0x0A4

CTIOUTEN1

RW

0x0A8

CTIOUTEN2

RW

0x0AC

CTIOUTEN3

RW

0x0B0

CTIOUTEN4

RW

0x0B4

CTIOUTEN5

RW

0x0B8

CTIOUTEN6

RW

0x0BC

CTIOUTEN7

RW

0x0C0-0x12C

-

-

Reserved

0x130

CTITRIGINSTATUS

RO

CTI Trigger In Status Register

0x134

CTITRIGOUTSTATUS RO

CTI Trigger Out Status Register

0x138

CTICHINSTATUS

RO

CTI Channel In Status Register

0x13C

CTICHOUTSTATUS

RO

CTI Channel Out Status Register

0x140

CTIGATE

RW

CTI Channel Gate Enable Register

C12 CTI registers

C12.1 Cross trigger register summary

100236_0100_00_en

Copyright © 2015–2017, 2019 Arm Limited or its affiliates. All rights

reserved.

C12-826

Non-Confidential

Summary of Contents for Cortex-A35

Page 4: ......

Page 18: ......

Page 26: ......

Page 27: ...Part A Functional Description ...

Page 28: ......

Page 145: ...Part B Register Descriptions ...

Page 146: ......

Page 573: ...Part C Debug ...

Page 574: ......

Page 845: ...Part D Appendices ...

Page 846: ......