System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-137

ID021414

Non-Confidential

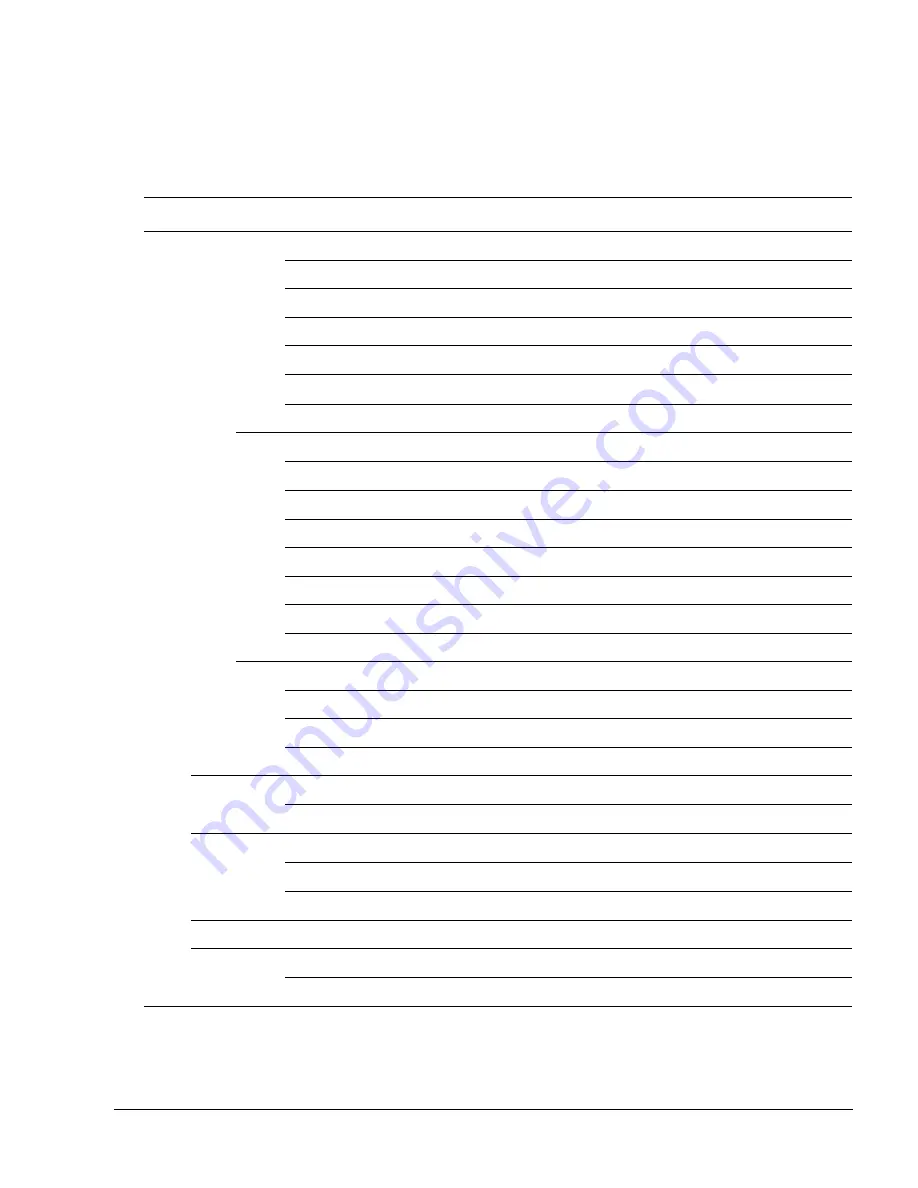

4.4.1

c0 registers

Table 4-122

shows the 32-bit wide system registers you can access when the processor is in

AArch32 state and the value of CRn is c0.

Table 4-122 c0 register summary

CRn

Op1

CRm

Op2

Name

Reset

Description

c0

0

c0

0

MIDR

0x410FD032

Main ID Register

on page 4-157

1

CTR

0x84448004

Cache Type Register

on page 4-188

2

TCMTR

0x00000000

TCM Type Register

on page 4-160

3

TLBTR

0x00000000

TLB Type Register

on page 4-160

4, 7

MIDR

0x410FD032

Aliases of Main ID Register,

Main ID Register

on page 4-157

5

MPIDR

-

a

Multiprocessor Affinity Register

on page 4-158

6

REVIDR

0x00000000

Revision ID Register

on page 4-159

c1

0

ID_PFR0

0x00000131

Processor Feature Register 0

on page 4-160

1

ID_PFR1

0x10011011

b

Processor Feature Register 1

on page 4-162

2

ID_DFR0

0x03010066

Debug Feature Register 0

on page 4-163

3

ID_AFR0

0x00000000

Auxiliary Feature Register 0

on page 4-164

4

ID_MMFR0

0x10101105

Memory Model Feature Register 0

on page 4-165

5

ID_MMFR1

0x40000000

Memory Model Feature Register 1

on page 4-166

6

ID_MMFR2

0x01260000

Memory Model Feature Register 2

on page 4-168

7

ID_MMFR3

0x02102211

Memory Model Feature Register 3

on page 4-170

c2

0

ID_ISAR0

0x02101110

Instruction Set Attribute Register 0

on page 4-172

1

ID_ISAR1

0x13112111

Instruction Set Attribute Register 1

on page 4-173

2

ID_ISAR2

0x21232042

Instruction Set Attribute Register 2

on page 4-175

3

ID_ISAR3

0x01112131

Instruction Set Attribute Register 3

on page 4-178

0

c2

4

ID_ISAR4

0x00011142

Instruction Set Attribute Register 4

on page 4-179

5

ID_ISAR5

0x00011121

c

Instruction Set Attribute Register 5

on page 4-181

1

c0

0

CCSIDR

-

Cache Size ID Register

on page 4-183

1

CLIDR

0x0A200023

d

Cache Level ID Register

on page 4-185

7

AIDR

0x00000000

Auxiliary ID Register

on page 4-187

2

c0

0

CSSELR

0x00000000

Cache Size Selection Register

on page 4-187

4

c0

0

VPIDR

0x410FD032

Virtualization Processor ID Register

on page 4-189

5

VMPIDR

-

e

Virtualization Multiprocessor ID Register

on page 4-190

a. The reset value depends on the primary inputs, CLUSTERIDAFF1 and CLUSTERIDAFF2, and the number of cores that the device

implements.

b. Bits [31:28] are

0x1

if the GIC CPU interface is enabled,

and 0x0

otherwise.

c. ID_ISAR5 has the value

0x00010001

if the Cryptography Extension is not implemented and enabled.