System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-155

ID021414

Non-Confidential

4.4.27

AArch32 Generic Timer registers

See

Chapter 10

Generic Timer

for information on the timer registers.

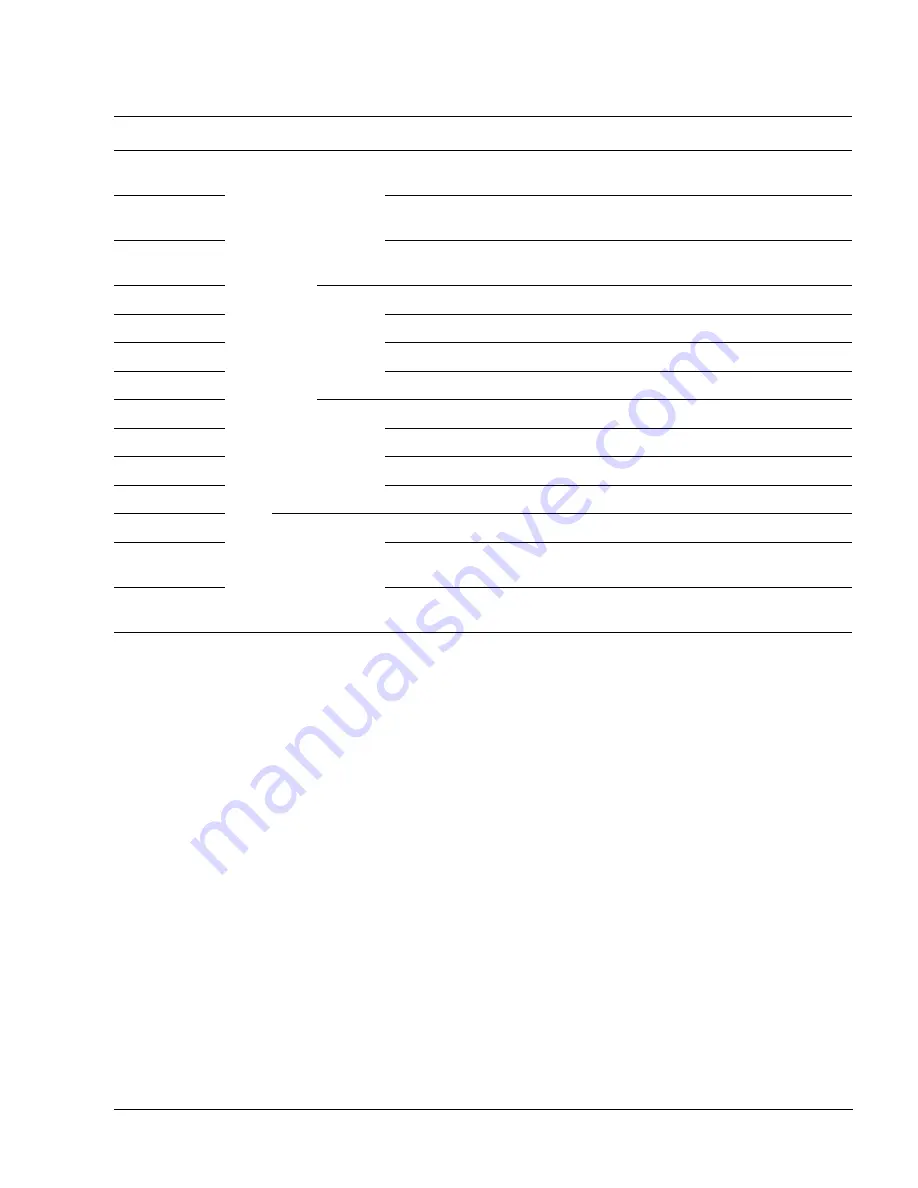

ICH_EISR

c12

4

c8

3

RO

0x00000000

32-bit

Interrupt Controller End of Interrupt

Status Register

ICH_VMCR

7

RW

0x004C0000

32-bit

Interrupt Controller Virtual Machine

Control Register

ICH_ELSR

5

RO

0x0000000F

32-bit

Interrupt Controller Empty List

Register Status Register

ICH_LR0

c12

0

RW

0x00000000

32-bit

Interrupt Controller List Register 0

ICH_LR1

1

RW

0x00000000

32-bit

Interrupt Controller List Register 1

ICH_LR1

2

RW

0x00000000

32-bit

Interrupt Controller List Register 2

ICH_LR1

3

RW

0x00000000

32-bit

Interrupt Controller List Register 3

ICH_LRC0

c14

0

RW

0x00000000

32-bit

Interrupt Controller List Register 0

ICH_LRC1

1

RW

0x00000000

32-bit

Interrupt Controller List Register 1

ICH_LRC2

2

RW

0x00000000

32-bit

Interrupt Controller List Register 2

ICH_LRC3

3

RW

0x00000000

32-bit

Interrupt Controller List Register 3

ICC_MCTLR

6

c12

4

RW

0x00000400

32-bit

Interrupt Control Register for EL3

ICC_MSRE

5

RW

0x00000000

32-bit

System Register Enable Register for

EL3

ICC_MGRPEN1

7

RW

0x00000000

32-bit

Interrupt Controller Monitor Interrupt

Group 1 Enable register

a. This is the reset value in non-secure state. In secure state, the reset value is 0x00000002.

Table 4-146 AArch32 GIC system registers (continued)

Name

CRn

Op1

CRm

Op2

Type

Reset Width

Description