System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-254

ID021414

Non-Confidential

Usage constraints

This register is accessible as follows:

The L2ECTLR can be written dynamically.

Configurations

L2ECTLR is architecturally mapped o the AArch64 L2ECTLR_EL1

register. See

L2 Extended Control Register

on page 4-107

.

There is one copy of this register that is used in both Secure and

Non-secure states.

There is one L2ECTLR for the Cortex-A53 processor.

Attributes

L2ECTLR is a 32-bit register.

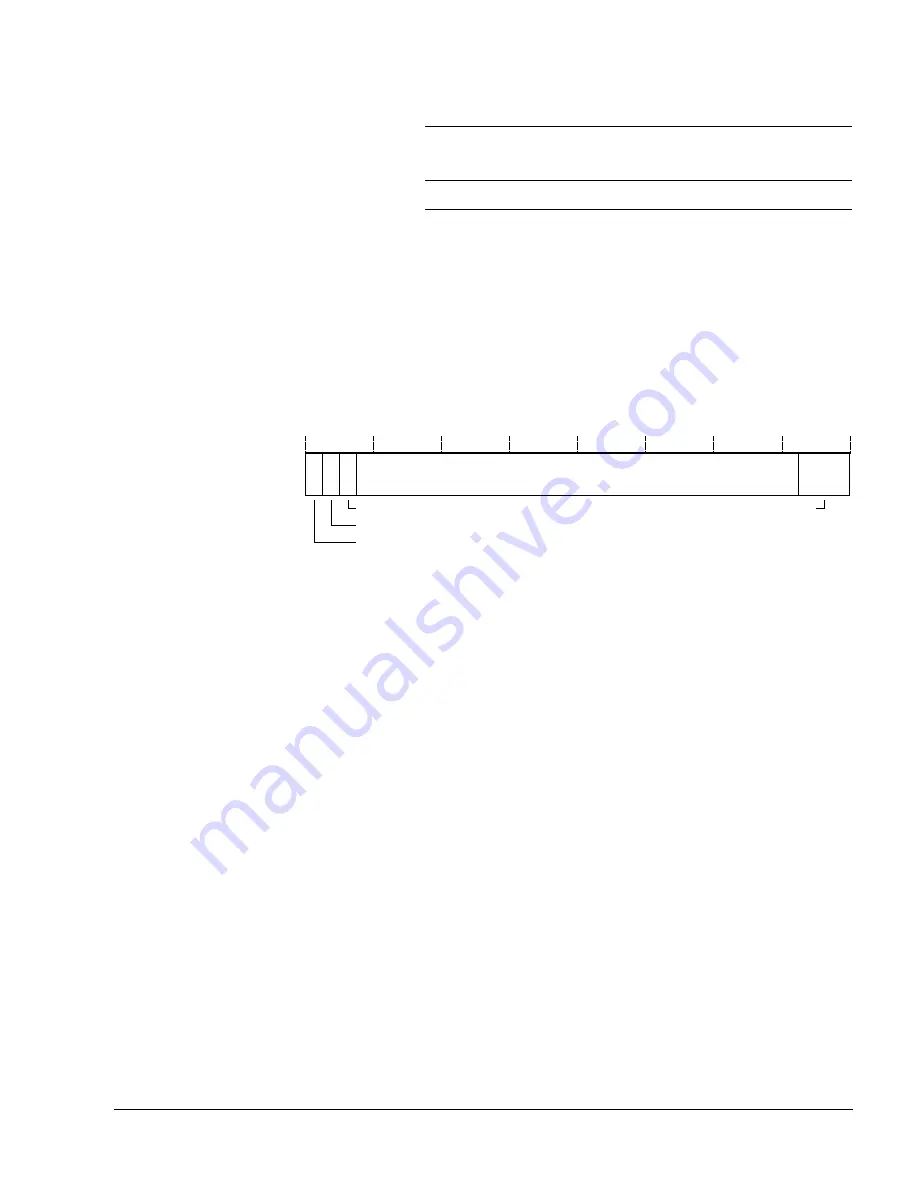

Figure 4-132

shows the L2ECTLR bit assignments.

Figure 4-132 L2ECTLR bit assignments

EL0

(NS)

EL0

(S)

EL1

(NS)

EL1

(S)

EL2

EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

-

-

RW

RW

RW

RW

RW

31

0

30

28

RES

0

RES

0

29

L2 internal asynchronous error

1

2

3

AXI or AMBA 5 CHI asynchronous error

L2 dynamic retention control