Embedded Trace Macrocell

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

13-45

ID021414

Non-Confidential

The TRCIDR5 can be accessed through the internal memory-mapped interface and the external

debug interface, offset

0x1F4

.

13.8.37 Resource Selection Control Registers 2-16

The TRCRSCTLRn characteristics are:

Purpose

Controls the trace resources.

There are eight resource pairs, the first pair is predefined as {0,1,pair=0}

and having reserved select registers. This leaves seven pairs to be

implemented as programmable selectors.

Usage constraints

Accepts writes only when the trace unit is disabled.

Configurations

Available in all configurations.

Attributes

See the register summary in

Table 13-3 on page 13-10

.

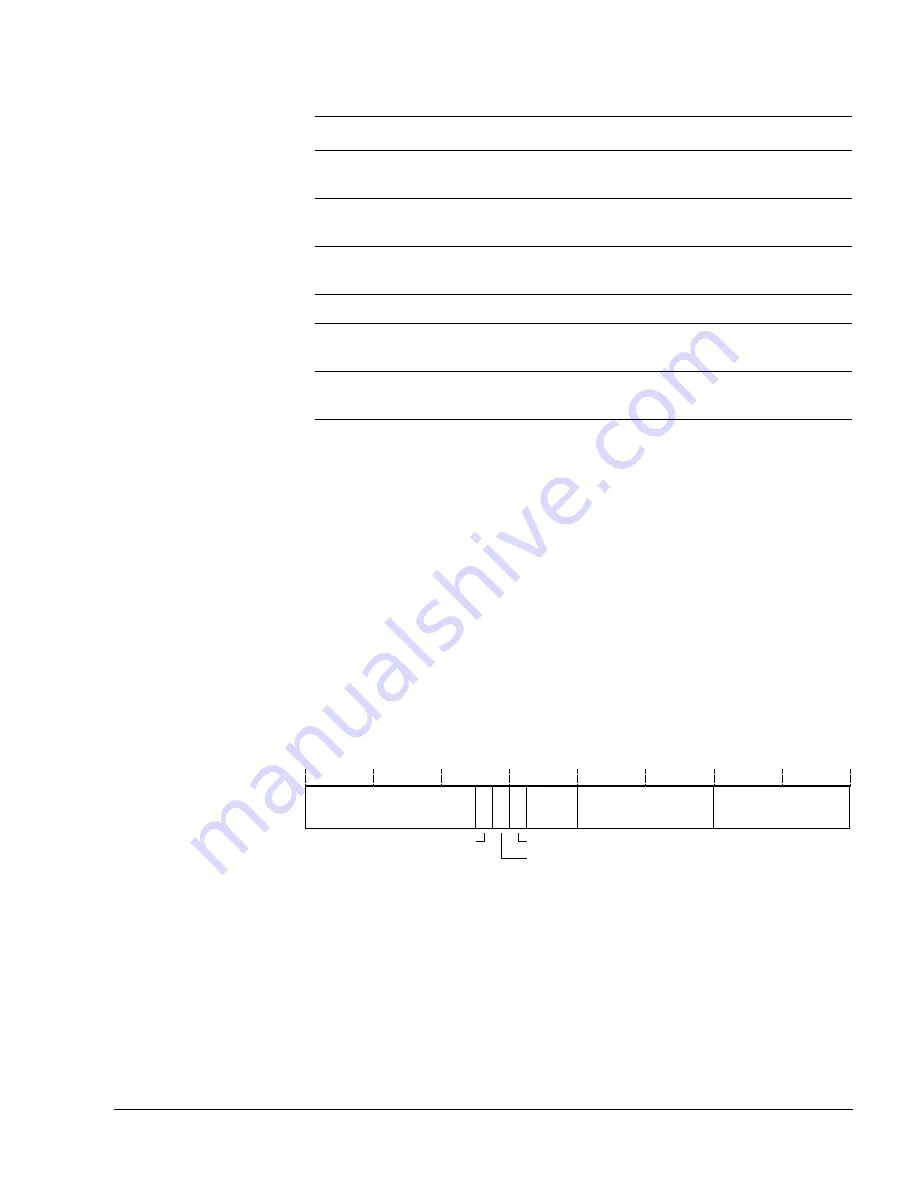

Figure 13-39

shows the TRCRSCTLRn bit assignments.

Figure 13-39 TRCRSCTLRn bit assignments

[23]

LPOVERRIDE

Low power state override support:

1

Low power state override support implemented.

[22]

ATBTRIG

ATB trigger support:

1

ATB trigger support implemented.

[21:16]

TRACEIDSIZE

Number of bits of trace ID:

0x07

Seven-bit trace ID implemented.

[15:12]

-

Reserved,

RES

0.

[11:9]

NUMEXTINSEL

Number of external input selectors implemented:

b100

Four external input selectors implemented.

[8:0]

NUMEXTIN

Number of external inputs implemented:

0x1E

30 external inputs implemented.

Table 13-39 TRCIDR5 bit assignments (continued)

Bits

Name

Function

31

0

RES

0

16 15

20 19

INV

PAIRINV

22 21

Select

Group

18

RES

0

RES

0

8 7