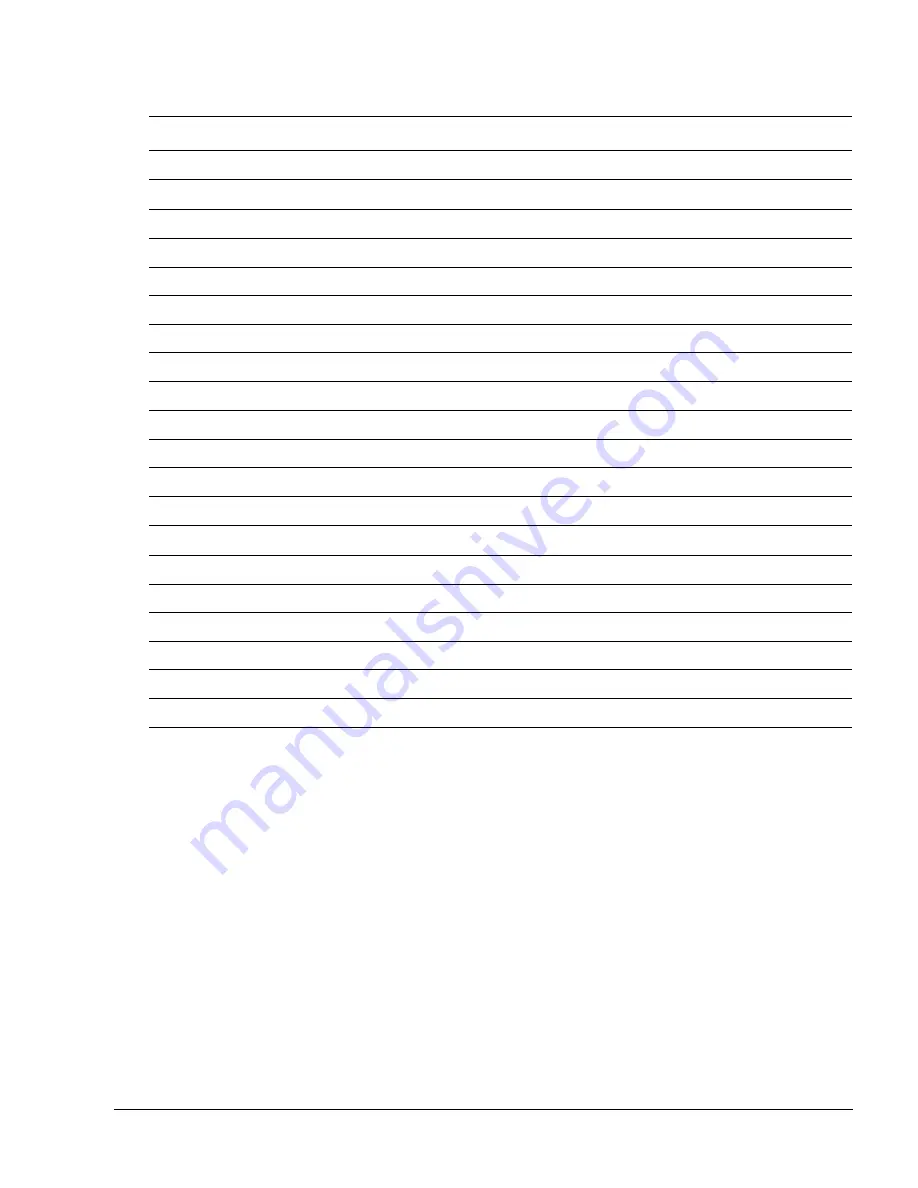

System Control

ARM DDI 0500D

Copyright © 2013-2014 ARM. All rights reserved.

4-4

ID021414

Non-Confidential

ID_ISAR4_EL1

RO

0x00011142

32

AArch32 Instruction Set Attribute Register 4

on page 4-34

ID_ISAR5_EL1

RO

0x00011121

c

32

AArch32 Instruction Set Attribute Register 5

on page 4-36

ID_AA64PFR0_EL1

RO

0x01002222

de

64

AArch64 Processor Feature Register 0

on page 4-37

ID_AA64PFR1_EL1

RO

0x00000000

64

AArch64 Processor Feature Register 1

ID_AA64DFR0_EL1

RO

0x10305106

64

AArch64 Debug Feature Register 0, EL1

on page 4-39

ID_AA64DFR1_EL1

RO

0x00000000

64

AArch64 Debug Feature Register 1

ID_AA64AFR0_EL1

RO

0x00000000

64

AArch64 Auxiliary Feature Register 0

ID_AA64AFR1_EL1

RO

0x00000000

64

AArch64 Auxiliary Feature Register 1

ID_AA64ISAR0_EL1

RO

0x00011120

f

64

AArch64 Instruction Set Attribute Register 0, EL1

on page 4-40

ID_AA64ISAR1_EL1

RO

0x00000000

64

AArch64 Instruction Set Attribute Register 1

ID_AA64MMFR0_EL1

RO

0x00001122

64

AArch64 Memory Model Feature Register 0, EL1

on page 4-41

ID_AA64MMFR1_EL1

RO

0x00000000

64

AArch64 Memory Model Feature Register 1

CCSIDR_EL1

RO

-

g

32

Cache Size ID Register

on page 4-43

CLIDR_EL1

RO

0x0A200023

h

32

Cache Level ID Register

on page 4-44

AIDR_EL1

RO

0x00000000

32

Auxiliary ID Register

on page 4-45

CSSELR_EL1

RW

0x00000000

32

Cache Size Selection Register

on page 4-45

CTR_EL0

RO

0x84448004

32

Cache Type Register

on page 4-47

DCZID_EL0

RO

0x00000004

32

Data Cache Zero ID Register

on page 4-48

VPIDR_EL2

RW

0x410FD032

32

Virtualization Processor ID Register

on page 4-49

VMPIDR_EL2

RO

-

i

64

Virtualization Multiprocessor ID Register

on page 4-50

a. The reset value depends on the primary inputs, CLUSTERIDAFF1 and CLUSTERIDAFF2, and the number of cores that the device

implements.

b. Bits [31:28] are

0x1

if the GIC CPU interface is enabled,

and 0x0

otherwise.

c. ID_ISAR5_EL1 has the value

0x00010001

if the Cryptography Extension is not implemented and enabled.

d. Bits [27:24] are

0x1

if the GIC CPU interface is enabled,

and 0x0

otherwise.

e. Bits [23:16] are

0x00

if the Advanced SIMD and Floating-point Extension is implemented, and

0xFF

otherwise.

f. ID_AA64ISAR0_EL1 has the value

0x00010000

if the Cryptography Extension is not implemented and enabled.

g. The reset value depends on the implementation. See the register description for details.

h. The value is

0x09200003

if the L2 cache is not implemented.

i. The reset value is the value of the Multiprocessor Affinity Register.

Table 4-1 AArch64 identification registers (continued)

Name

Type

Reset

Width

Description