A8.7

Error injection

To support testing of error handling software, the Cortex-A76 core can inject errors in the error detection

logic.

The following table describes all the possible types of error that the core can encounter and therefore

inject.

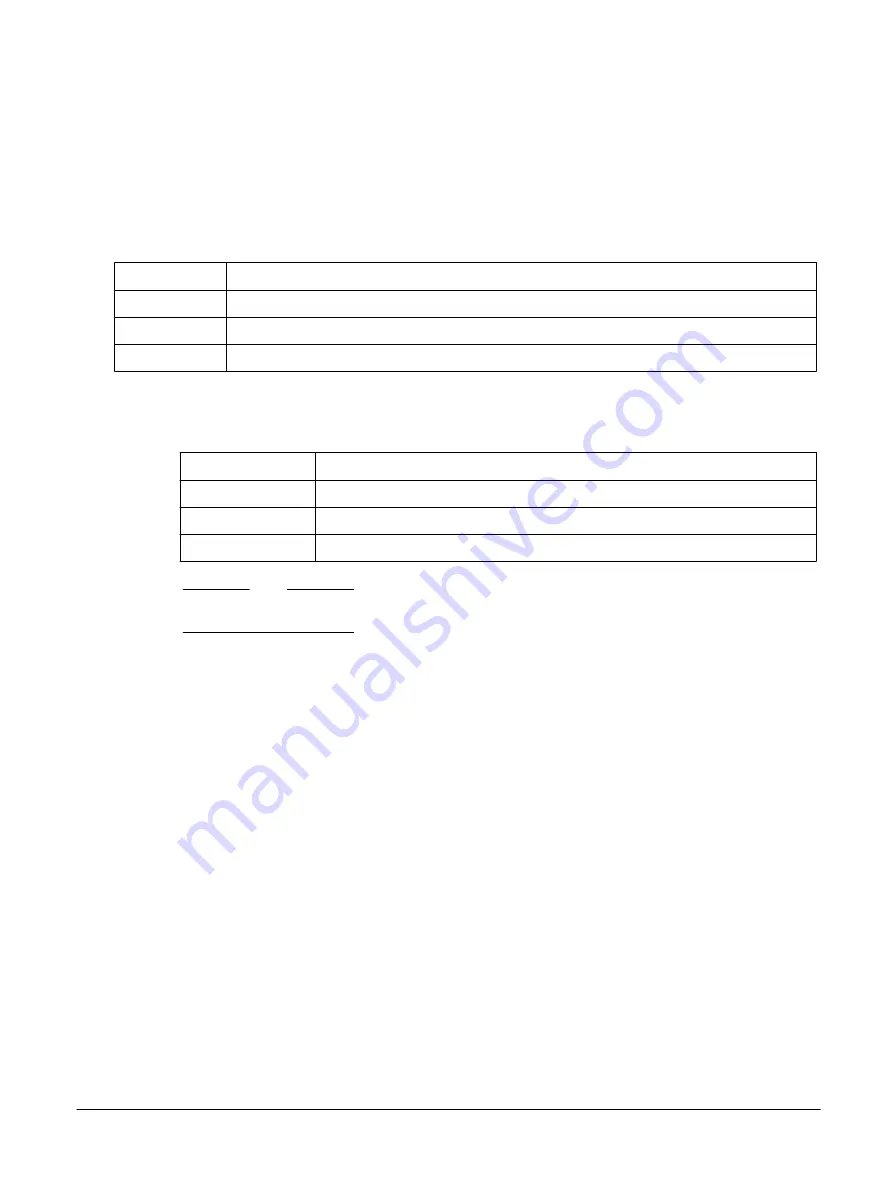

Table A8-3 Errors injected in the Cortex-A76 core

Error type

Description

Corrected errors

A CE is generated for a single-bit ECC error on L1 data caches and L2 caches, both on data and tag RAMs.

Deferred errors

A DE is generated for a double-bit ECC error on L1 data caches and L2 caches, but only on data RAM.

Uncorrected errors A UE is generated for a double-bit ECC error on L1 data caches and L2 caches, but only on tag RAM.

The following table describes the registers that handle error injection in the Cortex-A76 core.

Table A8-4 Error injection registers

Register name

Description

ERR0PFGFR_EL1

The ERR Pseudo Fault Generation Feature register defines which errors can be injected.

ERR0PFGCTLR_EL1 The ERR Pseudo Fault Generation Control register controls the errors that are injected.

ERR0PFGCDNR_EL1 The ERR Pseudo Fault Generation Count Down register controls the fault injection timing.

Note

This mechanism simulates the corruption of any RAM but the data is not actually corrupted.

See also:

•

B3.9 ERR0PFGFR, Error Pseudo Fault Generation Feature Register

•

B3.8 ERR0PFGCTLR, Error Pseudo Fault Generation Control Register

.

•

B3.7 ERR0PFGCDNR, Error Pseudo Fault Generation Count Down Register

A8 Reliability, Availability, and Serviceability (RAS)

A8.7 Error injection

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A8-109

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......