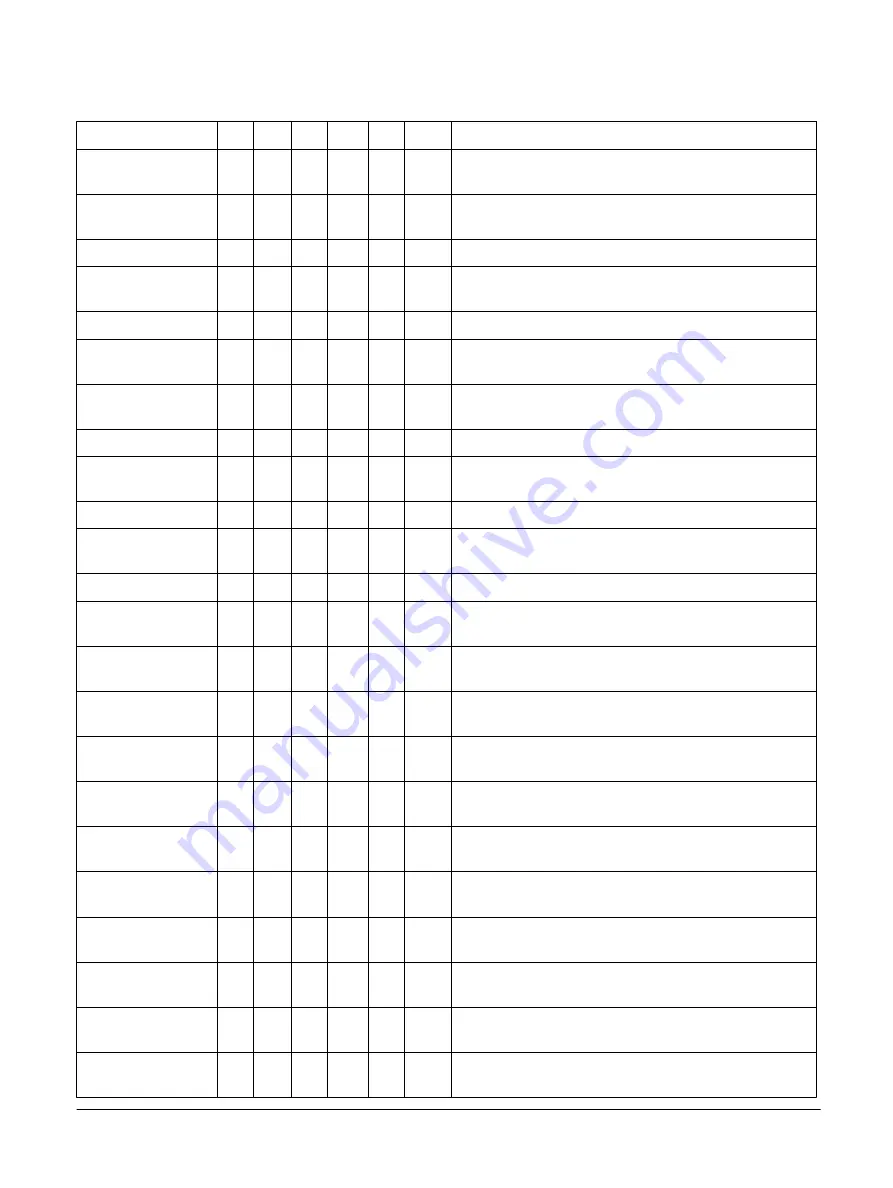

Table B2-1 Registers with implementation defined bit fields (continued)

Name

Op0 CRn Op1 CRm Op2 Width Description

ID_AA64MMFR2_EL1 3

c0

0

c7

2

64

B2.60 ID_AA64MMFR2_EL1, AArch64 Memory Model Feature

Register 2, EL1

ID_AA64PFR0_EL1

3

c0

0

c4

0

64

B2.61 ID_AA64PFR0_EL1, AArch64 Processor Feature Register

0, EL1

IFSR32_EL2

3

c5

4

c0

1

32

LORC_EL1

3

c10

0

c4

3

64

B2.80 LORC_EL1, LORegion Control Register, EL1

LORID_EL1

3

c10

0

c4

7

64

B2.81 LORID_EL1, LORegion ID Register, EL1

LORN_EL1

3

c10

0

c4

2

64

B2.82 LORN_EL1, LORegion Number Register, EL1

MDCR_EL3

3

c1

6

c3

1

32

B2.83 MDCR_EL3, Monitor Debug Configuration Register, EL3

MIDR_EL1

3

c0

0

c0

0

32

B2.84 MIDR_EL1, Main ID Register, EL1

MPIDR_EL1

3

c0

0

c0

5

64

B2.85 MPIDR_EL1, Multiprocessor Affinity Register, EL1

PAR_EL1

3

c7

0

c4

0

64

B2.86 PAR_EL1, Physical Address Register, EL1

RVBAR_EL3

3

c12

6

c0

1

64

B2.89 RVBAR_EL3, Reset Vector Base Address Register, EL3

REVIDR_EL1

3

c0

0

c0

6

32

B2.87 REVIDR_EL1, Revision ID Register, EL1

SCTLR_EL1

3

c1

0

c0

0

32

B2.90 SCTLR_EL1, System Control Register, EL1

SCTLR_EL2

3

c1

4

c0

0

32

B2.91 SCTLR_EL2, System Control Register, EL2

SCTLR_EL12

3

c1

5

c0

0

32

B2.90 SCTLR_EL1, System Control Register, EL1

SCTLR_EL3

3

c1

6

c0

0

32

B2.92 SCTLR_EL3, System Control Register, EL3

TCR_EL1

3

c2

0

c0

2

64

B2.93 TCR_EL1, Translation Control Register, EL1

TCR_EL2

3

c2

4

c0

2

64

B2.94 TCR_EL2, Translation Control Register, EL2

TCR_EL3

3

c2

6

c0

2

64

B2.95 TCR_EL3, Translation Control Register, EL3

TTBR0_EL1

3

c2

0

c0

0

64

B2.96 TTBR0_EL1, Translation Table Base Register 0, EL1

TTBR0_EL2

3

c2

4

c0

0

64

B2.97 TTBR0_EL2, Translation Table Base Register 0, EL2

TTBR0_EL3

3

c2

6

c0

0

64

B2.98 TTBR0_EL3, Translation Table Base Register 0, EL3

TTBR1_EL1

3

c2

0

c0

1

64

B2.99 TTBR1_EL1, Translation Table Base Register 1, EL1

B2 AArch64 system registers

B2.2 AArch64 architectural system register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-130

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......