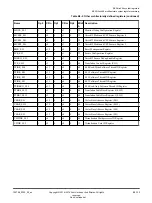

The following table shows the 32-bit wide implementation defined Cluster registers. Details of these

registers can be found in

Arm

®

DynamIQ

™

Shared Unit Technical Reference Manual

Table B2-5 Cluster registers

Name

Copro CRn Opc1 CRm Opc2 Width Description

CLUSTERCFR_EL1

3

c15

0

c3

0

32-bit Cluster configuration register.

CLUSTERIDR_EL1

3

c15

0

c3

1

32-bit Cluster main revision ID.

CLUSTEREVIDR_EL1

3

c15

0

c3

2

32-bit Cluster ECO ID.

CLUSTERACTLR_EL1

3

c15

0

c3

3

32-bit Cluster auxiliary control register.

CLUSTERECTLR_EL1

3

c15

0

c3

4

32-bit Cluster extended control register.

CLUSTERPWRCTLR_EL1

3

c15

0

c3

5

32-bit Cluster power control register.

CLUSTERPWRDN_EL1

3

c15

0

c3

6

32-bit Cluster power down register.

CLUSTERPWRSTAT_EL1

3

c15

0

c3

7

32-bit Cluster power status register.

CLUSTERTHREADSID_EL1

3

c15

0

c4

0

32-bit Cluster thread scheme ID register.

CLUSTERACPSID_EL1

3

c15

0

c4

1

32-bit Cluster ACP scheme ID register.

CLUSTERSTASHSID_EL1

3

c15

0

c4

2

32-bit Cluster stash scheme ID register.

CLUSTERPARTCR_EL1

3

c15

0

c4

3

32-bit Cluster partition control register.

CLUSTERBUSQOS_EL1

3

c15

0

c4

4

32-bit Cluster bus QoS control register.

CLUSTERL3HIT_EL1

3

c15

0

c4

5

32-bit Cluster L3 hit counter register.

CLUSTERL3MISS_EL1

3

c15

0

c4

6

32-bit Cluster L3 miss counter register.

CLUSTERTHREADSIDOVR_EL1 3

c15

0

c4

7

32-bit Cluster thread scheme ID override register

CLUSTERPMCR_EL1

3

c15

0

c5

0

32-bit Cluster Performance Monitors Control Register

CLUSTERPMCNTENSET_EL1

3

c15

0

c5

1

32-bit Cluster Count Enable Set Register

CLUSTERPMCNTENCLR_EL1

3

c15

0

c5

2

32-bit Cluster Count Enable Clear Register

CLUSTERPMOVSSET_EL1

3

c15

0

c5

3

32-bit Cluster Overflow Flag Status Set

CLUSTERPMOVSCLR_EL1

3

c15

0

c5

4

32-bit Cluster Overflow Flag Status Clear

CLUSTERPMSELR_EL1

3

c15

0

c5

5

32-bit Cluster Event Counter Selection Register

CLUSTERPMINTENSET_EL1

3

c15

0

c5

6

32-bit Cluster Interrupt Enable Set Register

CLUSTERPMINTENCLR_EL1

3

c15

0

c5

7

32-bit Cluster Interrupt Enable Clear Register

CLUSTERPMXEVTYPER_EL1

3

c15

0

c6

1

32-bit Cluster Selected Event Type and Filter Register

CLUSTERPMXEVCNTR_EL1

3

c15

0

c6

2

32-bit Cluster Selected Event Counter Register

Reserved/RAZ

3

c15

0

c6

3

32-bit Cluster Monitor Debug Configuration Register

CLUSTERPMCEID0_EL1

3

c15

0

c6

4

32-bit Cluster Common Event Identification ID0

Register

CLUSTERPMCEID1_EL1

3

c15

0

c6

5

32-bit Cluster Common Event Identification ID1

Register

B2 AArch64 system registers

B2.4 AArch64 registers by functional group

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-142

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......