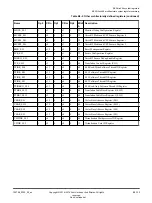

Table B2-5 Cluster registers (continued)

Name

Copro CRn Opc1 CRm Opc2 Width Description

CLUSTERPMCLAIMSET_EL1

3

c15

0

c6

6

32-bit Cluster Performance Monitor Claim Tag Set

Register

CLUSTERPMCLAIMCLR_EL1

3

c15

0

c6

7

32-bit Cluster Performance Monitor Claim Tag Clear

Register

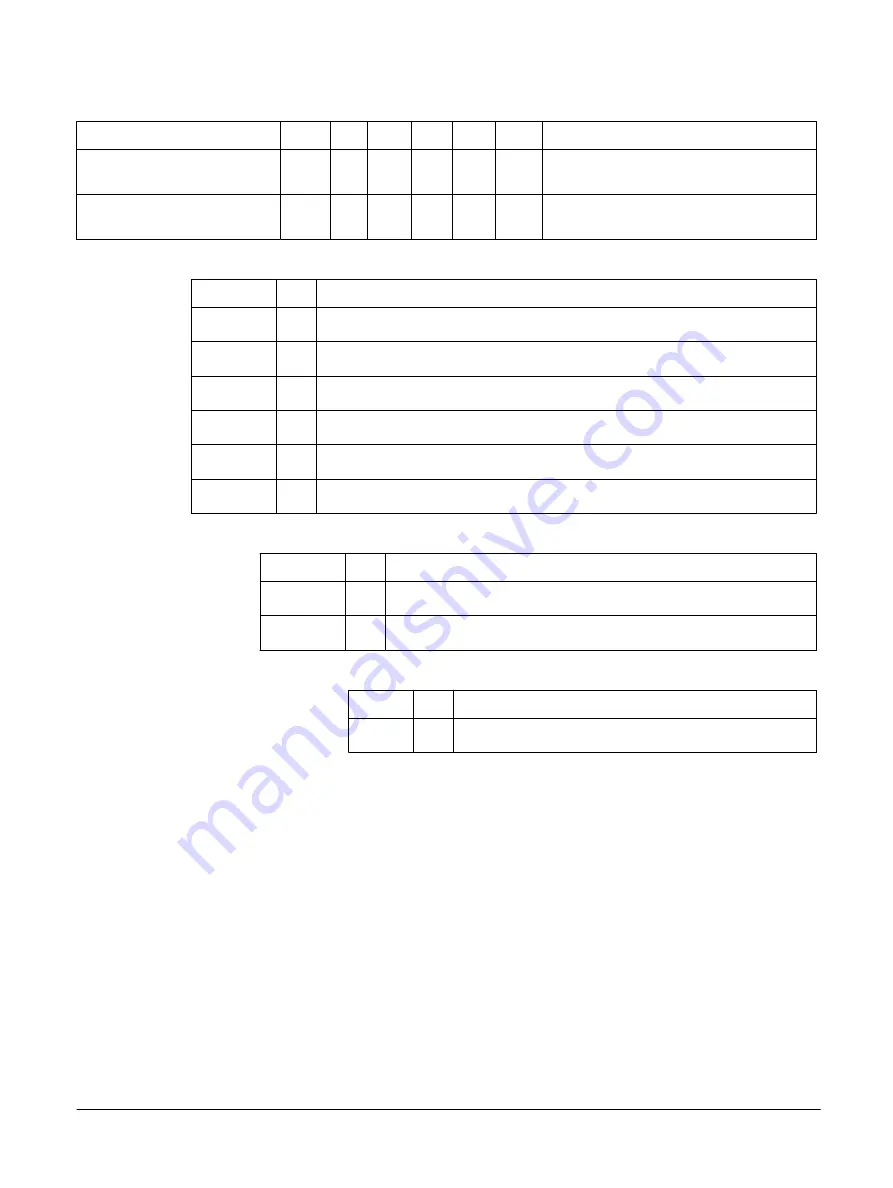

Security

Name

Type Description

ACTLR_EL3 RW

B2.7 ACTLR_EL3, Auxiliary Control Register, EL3

AFSR0_EL3 RW

B2.10 AFSR0_EL3, Auxiliary Fault Status Register 0, EL3

AFSR1_EL3 RW

B2.13 AFSR1_EL3, Auxiliary Fault Status Register 1, EL3

AMAIR_EL3 RW

B2.17 AMAIR_EL3, Auxiliary Memory Attribute Indirection Register, EL3

CPTR_EL3

RW

B2.22 CPTR_EL3, Architectural Feature Trap Register, EL3

MDCR_EL3

RW

B2.83 MDCR_EL3, Monitor Debug Configuration Register, EL3

Reset management registers

Name

Type Description

RMR_EL3

RW

B2.88 RMR_EL3, Reset Management Register

RVBAR_EL3 RW

B2.89 RVBAR_EL3, Reset Vector Base Address Register, EL3

Address registers

Name

Type Description

PAR_EL1 RW

B2.86 PAR_EL1, Physical Address Register, EL1

B2 AArch64 system registers

B2.4 AArch64 registers by functional group

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-143

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......