B5.1

AArch64 register summary

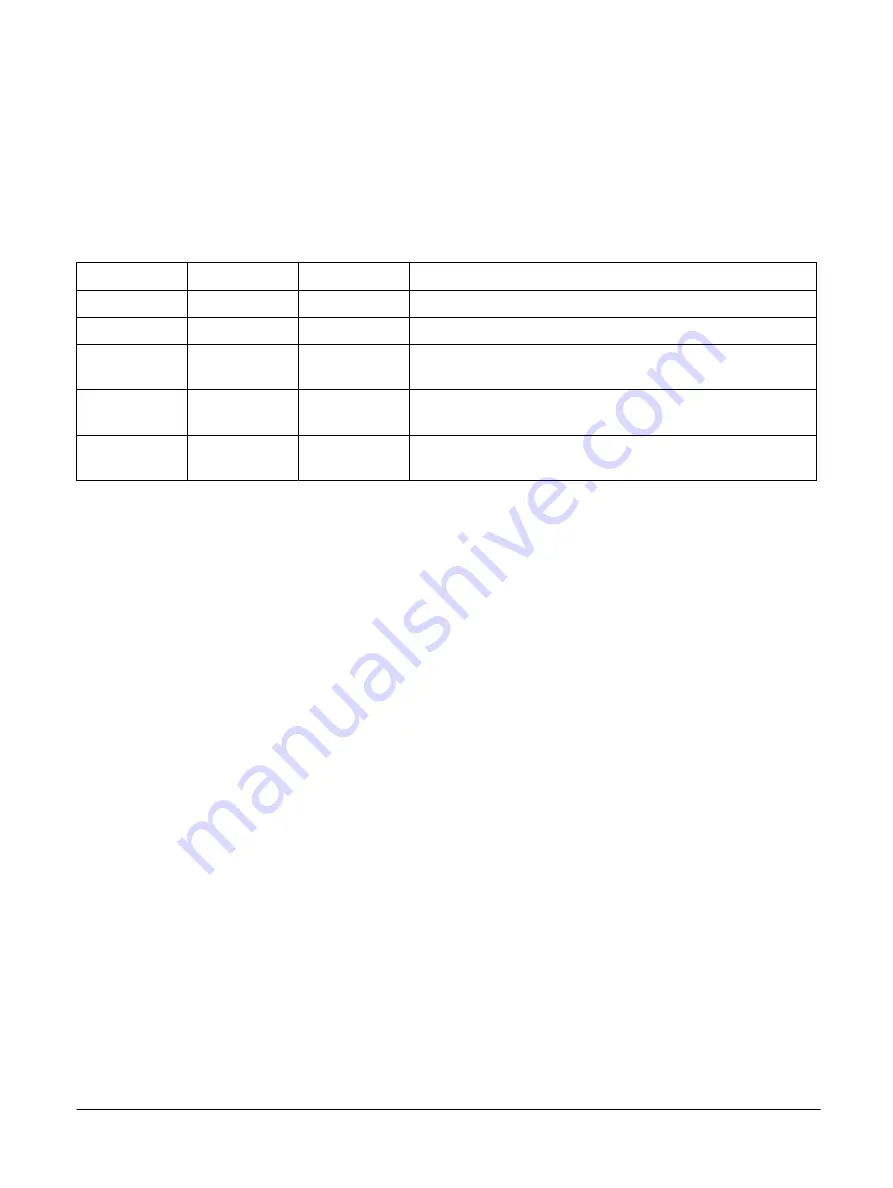

The core has several Advanced SIMD and floating-point system registers in the AArch64 execution

state. Each register has a specific purpose, specific usage constraints, configurations, and attributes.

The following table gives a summary of the Cortex-A76 core Advanced SIMD and floating-point system

registers in the AArch64 execution state.

Table B5-1 AArch64 Advanced SIMD and floating-point system registers

Name

Type

Reset

Description

FPCR

RW

0x00000000

B5.2 FPCR, Floating-point Control Register

FPSR

RW

UNKNOWN

B5.3 FPSR, Floating-point Status Register

.

MVFR0_EL1

RO

0x10110222

B5.4 MVFR0_EL1, Media and VFP Feature Register 0, EL1

MVFR1_EL1

RO

0x13211111

B5.5 MVFR1_EL1, Media and VFP Feature Register 1, EL1

MVFR2_EL1

RO

0x00000043

B5.6 MVFR2_EL1, Media and VFP Feature Register 2, EL1

B5 Advanced SIMD and floating-point registers

B5.1 AArch64 register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B5-346

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......