UFC, [3]

Underflow cumulative exception bit. This bit is set to 1 to indicate that the Underflow exception

has occurred since 0 was last written to this bit.

OFC, [2]

Overflow cumulative exception bit. This bit is set to 1 to indicate that the Overflow exception

has occurred since 0 was last written to this bit.

DZC, [1]

Division by Zero cumulative exception bit. This bit is set to 1 to indicate that the Division by

Zero exception has occurred since 0 was last written to this bit.

IOC, [0]

Invalid Operation cumulative exception bit. This bit is set to 1 to indicate that the Invalid

Operation exception has occurred since 0 was last written to this bit.

Configurations

The named fields in this register map to the equivalent fields in the AArch32 FPSCR. See

B5.8 FPSCR, Floating-Point Status and Control Register

.

Usage constraints

Accessing the FPSR

To access the FPSR:

MRS <Xt>, FPSR; Read FPSR into Xt

MSR FPSR, <Xt>; Write Xt to FPSR

Register access is encoded as follows:

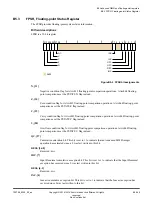

Table B5-3 FPSR access encoding

op0 op1 CRn CRm op2

11

011 0100 0100 001

Accessibility

This register is accessible as follows:

EL0 EL1

(NS)

EL1

(S)

EL2 EL3

(SCR.NS = 1)

EL3

(SCR.NS = 0)

RW RW

RW RW RW

RW

B5 Advanced SIMD and floating-point registers

B5.3 FPSR, Floating-point Status Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B5-350

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......