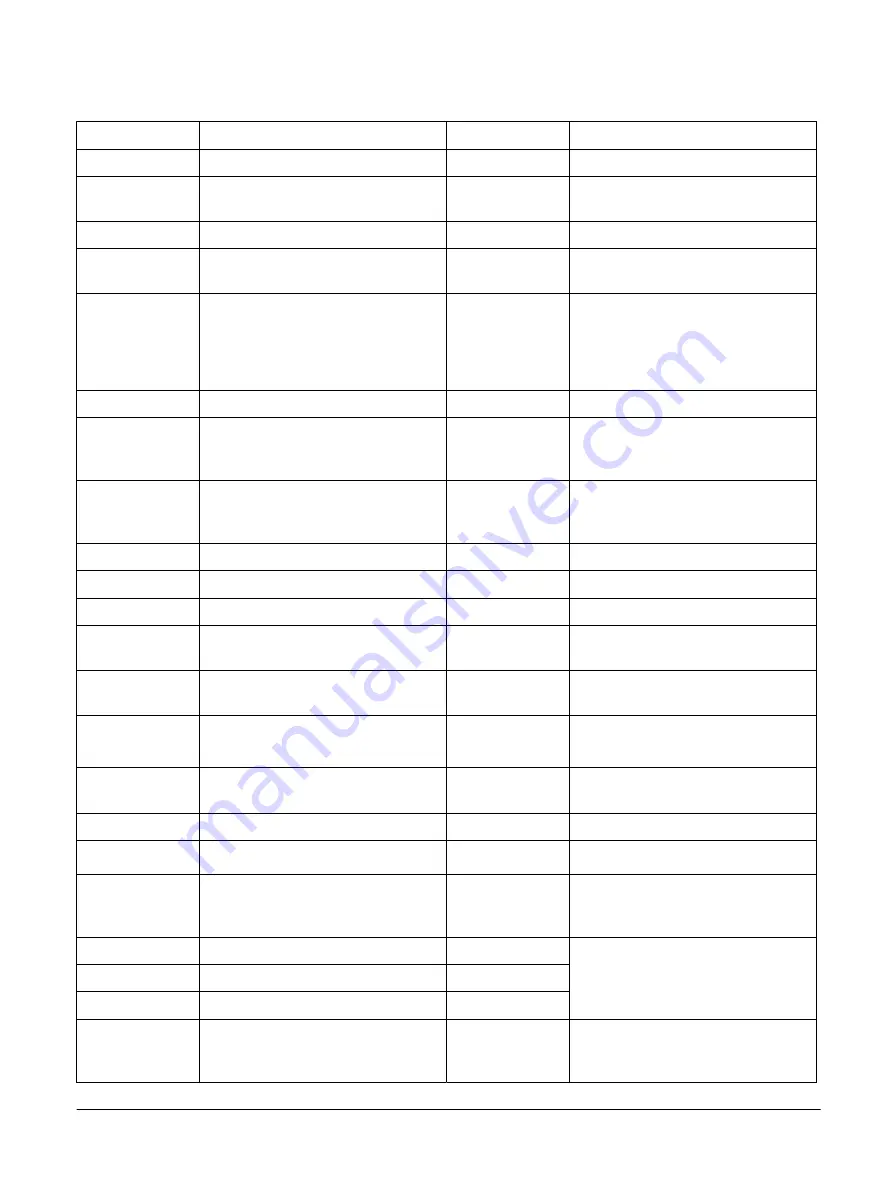

Table D6-1 Memory-mapped PMU register summary (continued)

Offset

Name

Type

Description

0xCA4-0xCBC

-

-

Reserved

0xCC0

PMOVSSET_EL0

RW

Performance Monitor Overflow Flag Status

Set Register

0xCC4-0xDFC

-

-

Reserved

0xE00

PMCFGR

RO

D6.2 PMCFGR, Performance Monitors

Configuration Register

0xE04

PMCR_EL0

RW

Performance Monitors Control Register.

This register is distinct from the

PMCR_EL0 system register. It does not

have the same value.

0xE08-0xE1C

-

-

Reserved

0xE20

PMCEID0

RO

D5.2 PMCEID0_EL0, Performance

Monitors Common Event Identification

Register 0, EL0

0xE24

PMCEID1

RO

D5.3 PMCEID1_EL0, Performance

Monitors Common Event Identification

Register 1, EL0

0xE28

PMCEID2

RO

0xE2C

PMCEID3

RO

0xFA4

-

-

Reserved

0xFA8

PMDEVAFF0

RO

B2.85 MPIDR_EL1, Multiprocessor

Affinity Register, EL1

0xFAC

PMDEVAFF1

RO

B2.85 MPIDR_EL1, Multiprocessor

Affinity Register, EL1

0xFB8

PMAUTHSTATUS

RO

Performance Monitor Authentication Status

Register

0xFBC

PMDEVARCH

RO

Performance Monitor Device Architecture

Register

0xFC0-0xFC8

-

-

Reserved

0xFCC

PMDEVTYPE

RO

Performance Monitor Device Type Register

0xFD0

PMPIDR4

RO

D6.11 PMPIDR4, Performance Monitors

Peripheral Identification Register 4

0xFD4

PMPIDR5

RO

D6.12 PMPIDRn, Performance Monitors

Peripheral Identification Register 5-7

0xFD8

PMPIDR6

RO

0xFDC

PMPIDR7

RO

0xFE0

PMPIDR0

RO

D6.7 PMPIDR0, Performance Monitors

Peripheral Identification Register 0

D6 Memory-mapped PMU registers

D6.1 Memory-mapped PMU register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D6-458

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......