D9.32

TRCIDR3, ID Register 3

The TRCIDR3 indicates:

• Whether TRCVICTLR is supported.

• The number of cores available for tracing.

• If an exception level supports instruction tracing.

• The minimum threshold value for instruction trace cycle counting.

• Whether the synchronization period is fixed.

• Whether TRCSTALLCTLR is supported and if so whether it supports trace overflow prevention and

supports stall control of the core.

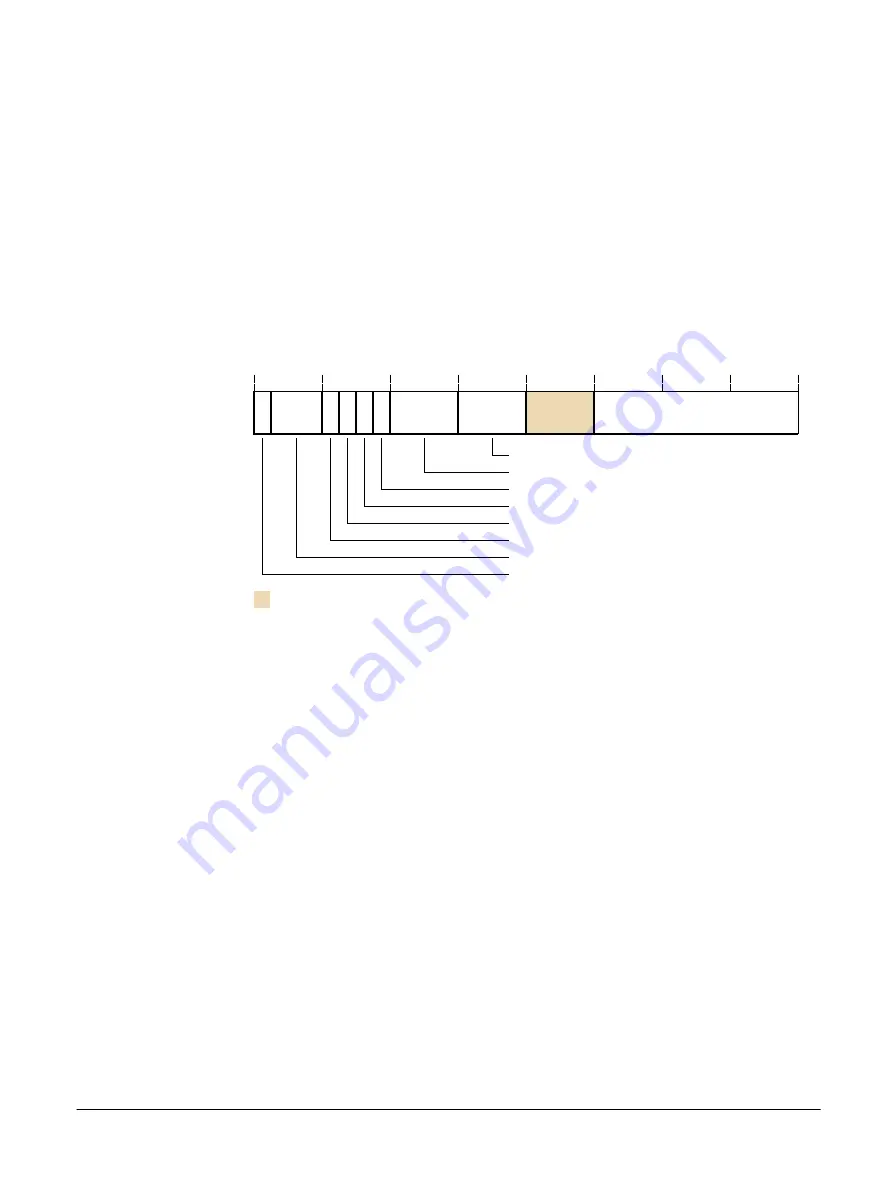

Bit field descriptions

The TRCIDR3 is a 32-bit register.

31

0

25 24

16 15

11

12

5 4

CCITMIN

30

28

20 19

23

27 26

EXLEVEL_S

EXLEVEL_NS

NOOVERFLOW

NUMPROC

SYSSTALL

STALLCTL

SYNCPR

TRCERR

RES

0

Figure D9-30 TRCIDR3 bit assignments

NOOVERFLOW, [31]

Indicates whether TRCSTALLCTLR.NOOVERFLOW is implemented:

0

TRCSTALLCTLR.NOOVERFLOW is not implemented.

NUMPROC, [30:28]

Indicates the number of cores available for tracing:

0b000

The trace unit can trace one core, ETM trace unit sharing not supported.

SYSSTALL, [27]

Indicates whether stall control is implemented:

1

The system supports core stall control.

STALLCTL, [26]

Indicates whether TRCSTALLCTLR is implemented:

1

TRCSTALLCTLR is implemented.

This field is used in conjunction with SYSSTALL.

SYNCPR, [25]

Indicates whether there is a fixed synchronization period:

D9 ETM registers

D9.32 TRCIDR3, ID Register 3

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-539

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......