D9.34

TRCIDR5, ID Register 5

The TRCIDR5 returns how many resources the trace unit supports.

Bit field descriptions

31

0

25 24

16 15

8

27

28

NUMEXTIN

TRACEIDSIZE

NUMEXTINSEL

9

11

12

ATBTRIG

30

23 22 21

LPOVERRIDE

NUMSEQSTATE

NUMCNTR

REDFUNCNTR

RES

0

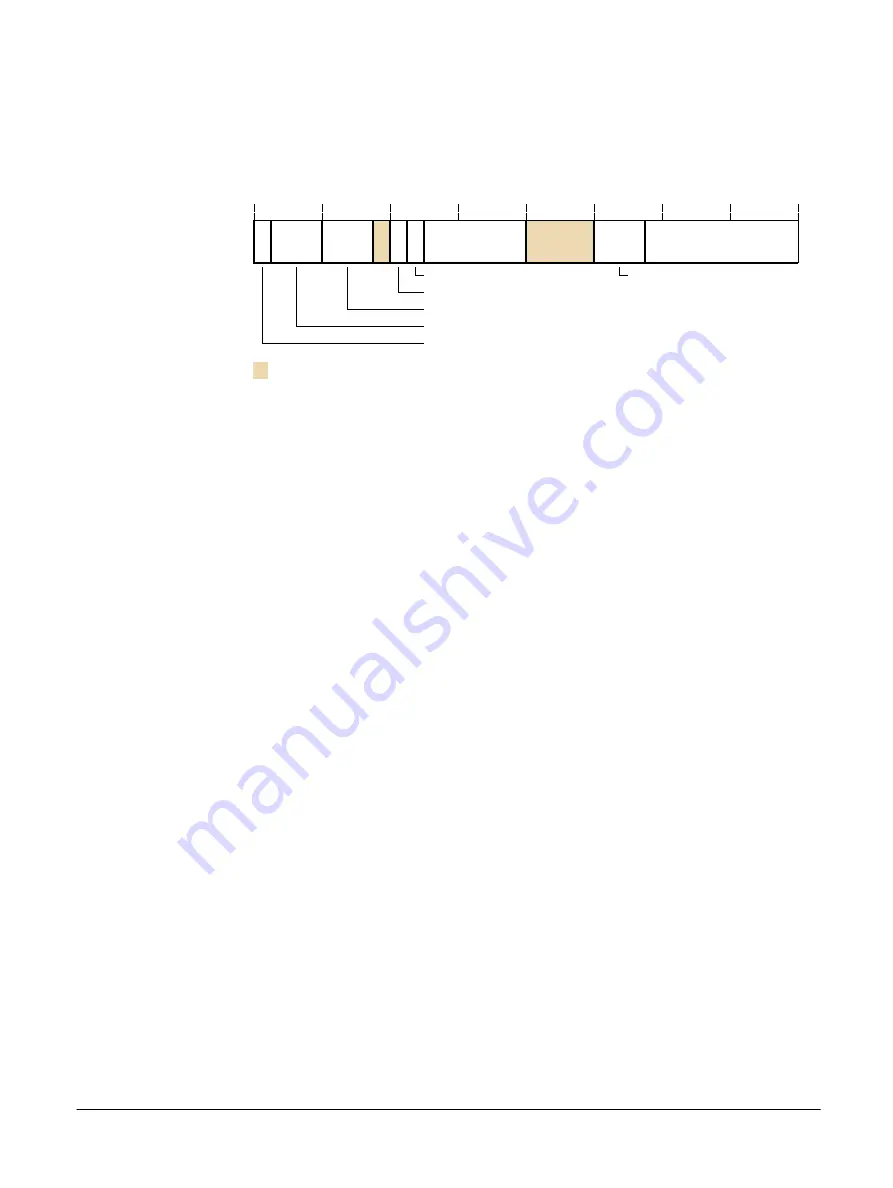

Figure D9-32 TRCIDR5 bit assignments

REDFUNCNTR, [31]

Reduced Function Counter implemented:

0

Reduced Function Counter not implemented.

NUMCNTR, [30:28]

Number of counters implemented:

0b010

Two counters implemented.

NUMSEQSTATE, [27:25]

Number of sequencer states implemented:

0b100

Four sequencer states implemented.

RES0, [24]

RES0

Reserved.

LPOVERRIDE, [23]

Low-power state override support:

1

Low-power state override support implemented.

ATBTRIG, [22]

ATB trigger support:

1

ATB trigger support implemented.

TRACEIDSIZE, [21:16]

Number of bits of trace ID:

0x07

Seven-bit trace ID implemented.

RES0, [15:12]

RES0

Reserved.

NUMEXTINSEL, [11:9]

D9 ETM registers

D9.34 TRCIDR5, ID Register 5

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-543

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......