A4.7

Encoding for power modes

The following table shows the encodings for the supported modes for each core domain P-Channel.

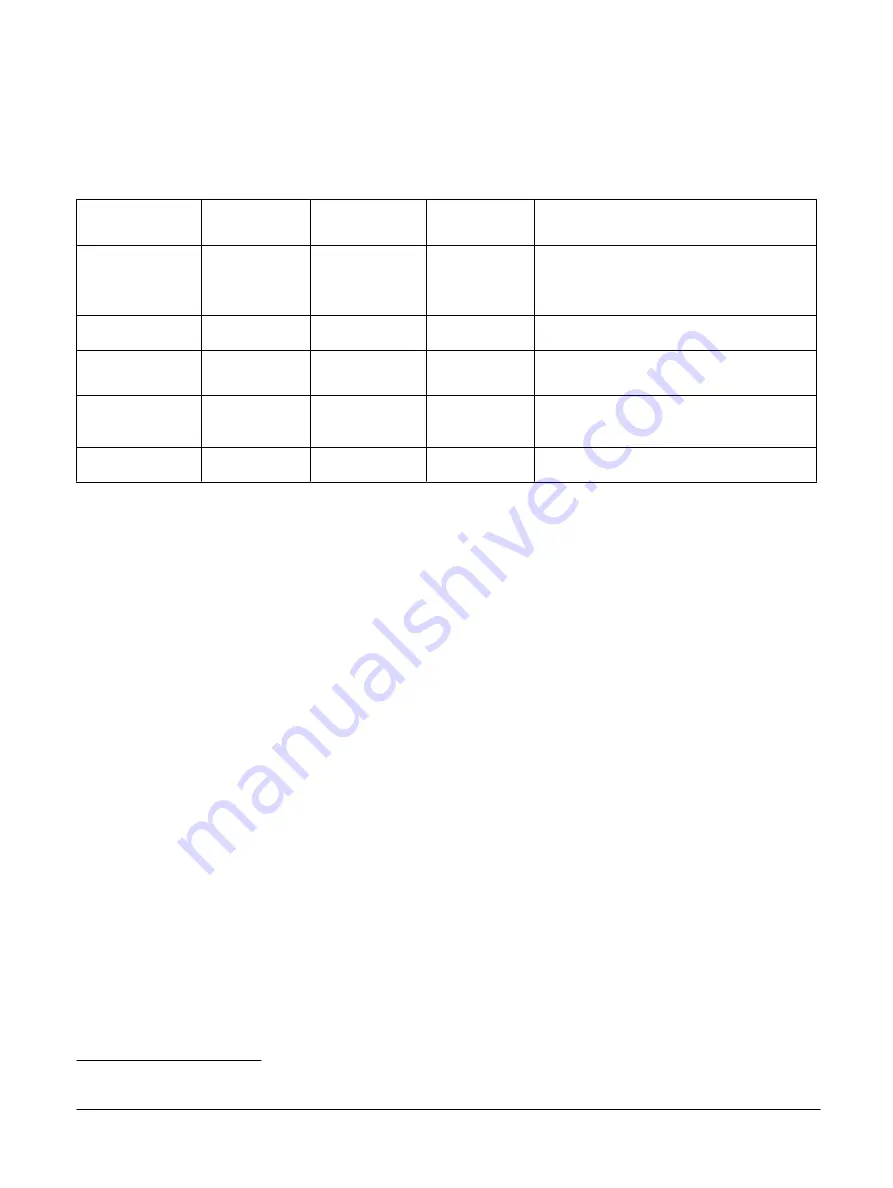

Table A4-2 Core power modes COREPSTATE encoding

Power mode

Short name

PACTIVE bit

number

PSTATE value

Power mode description

Debug recovery

DEBUG_RECOV -

0b001010

Logic is off (or in reset), RAM state is retained

and not invalidated when transitioning to On

mode.

On

ON

8

0b001000

All powerup.

Core dynamic

retention

FULL_RET

5

0b000101

Logic and RAM state are inoperable but retained.

Off (emulated)

OFF_EMU

1

0b000001

On with Warm reset asserted, debug state is

retained and accessible.

Off

OFF

0b000000

All powerdown.

PSTATE[5:4] are don't care.

It is tied off to 0 and should be inferred when all other PACTIVE bits are LOW. For more information, see the

AMBA

®

Low Power Interface Specification Arm

®

Q-

Channel and P-Channel Interfaces

.

A4 Power management

A4.7 Encoding for power modes

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A4-56

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......