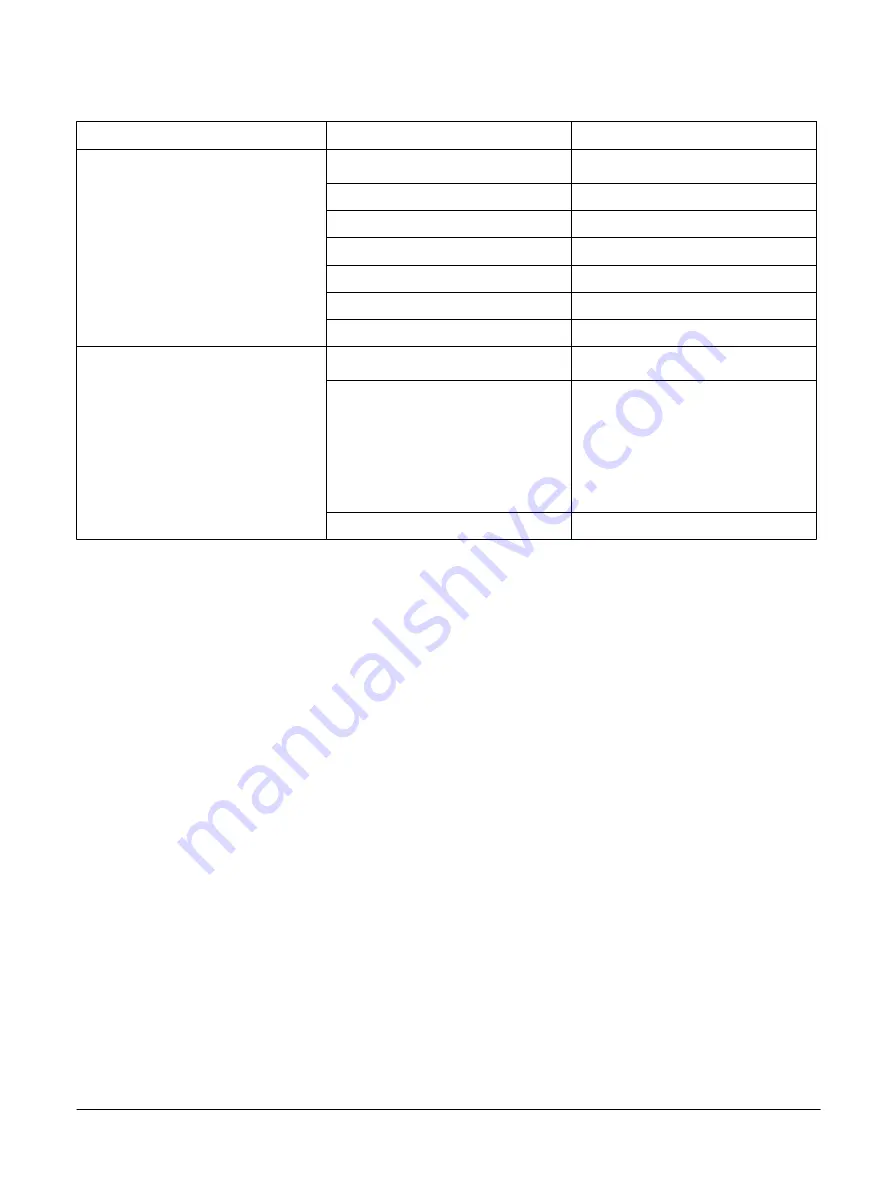

Table A6-31 L2 TLB format (continued)

Register

Bit field

Description

Instruction Register 1

[63:54]

VMID [9:0]

[53:38]

ASID [15:0]

[37]

Walk cache entry

[36]

Prefetched translation

[35:7]

Virtual address [48:20]

[6]

Non-secure

[5:0]

Reserved

Instruction Register 2

[63:8]

Reserved

[7:6]

Translation regime:

00

Secure EL1

01

EL3

10

Non-secure EL1

11

EL2

[5:0]

VMID [15:10]

A6 Level 1 memory system

A6.6 Direct access to internal memory

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A6-95

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......