B2.64

ID_DFR0_EL1, AArch32 Debug Feature Register 0, EL1

The ID_DFR0_EL1 provides top-level information about the debug system in AArch32.

Bit field descriptions

ID_DFR0_EL1 is a 32-bit register, and is part of the Identification registers functional group.

This register is Read Only.

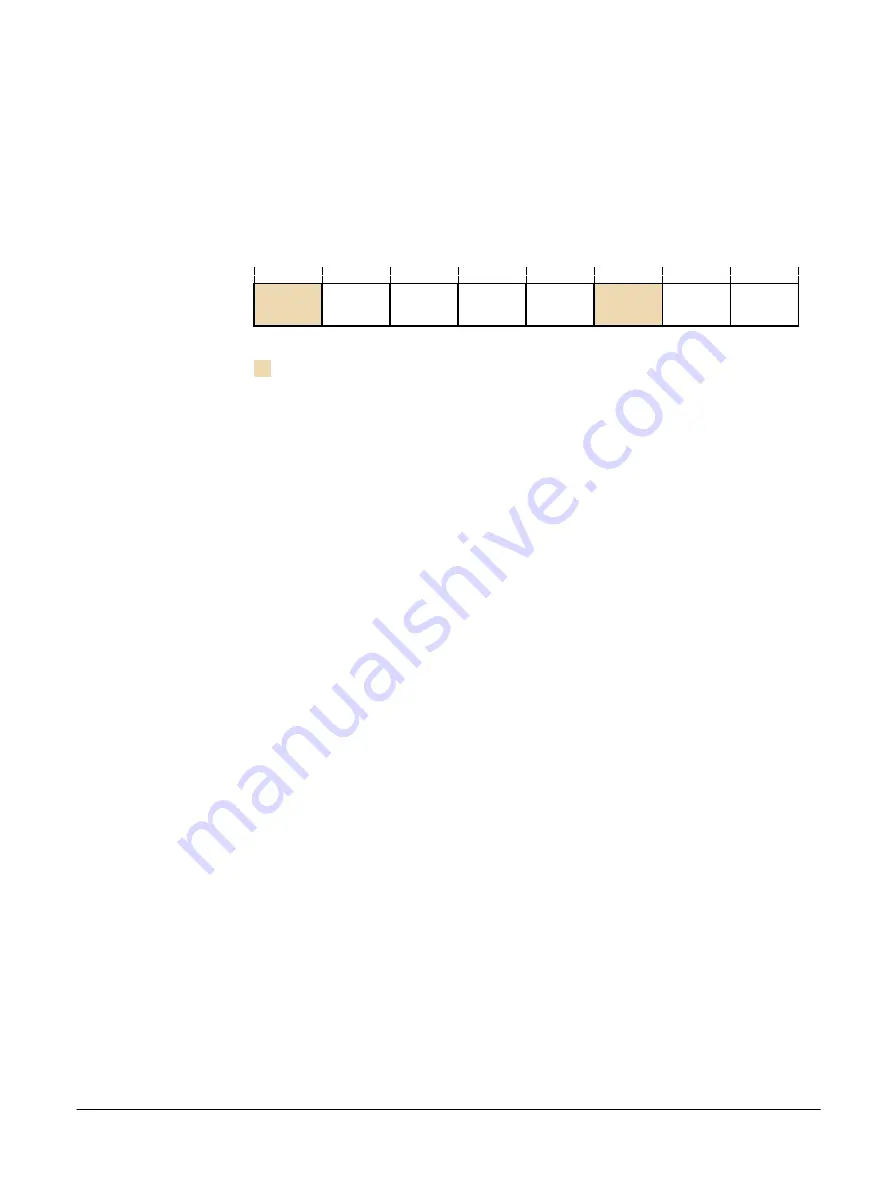

31

12 11

8 7

0

4 3

24 23

20 19

16 15

28 27

PerfMon

MProfDbg

MMapTrc

CopTrc

CopSDbg

CopDbg

RES

0

Figure B2-48 ID_DFR0_EL1 bit assignments

RES0, [31:28]

RES0

Reserved.

PerfMon, [27:24]

Indicates support for performance monitor model:

4

Support for

Performance Monitor Unit version 3

(PMUv3) system registers, with a

16-bit evtCount field.

MProfDbg, [23:20]

Indicates support for memory-mapped debug model for M profile cores:

0

This product does not support M profile Debug architecture.

MMapTrc, [19:16]

Indicates support for memory-mapped trace model:

1

Support for Arm trace architecture, with memory-mapped access.

In the Trace registers, the ETMIDR gives more information about the implementation.

CopTrc, [15:12]

Indicates support for coprocessor-based trace model:

0

This product does not support Arm trace architecture.

RES0, [11:8]

RES0

Reserved.

CopSDbg, [7:4]

Indicates support for coprocessor-based Secure debug model:

8

This product supports the Armv8.2 Debug architecture.

CopDbg, [3:0]

Indicates support for coprocessor-based debug model:

8

This product supports the Armv8.2 Debug architecture.

B2 AArch64 system registers

B2.64 ID_DFR0_EL1, AArch32 Debug Feature Register 0, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-231

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......