A1.1

About the core

The Cortex-A76 core is a high-performance and low-power Arm product that implements the Armv8-A

architecture.

The Cortex-A76 core supports:

• The Armv8.2-A extension.

• The RAS extension.

• The Load acquire (

LDAPR

) instructions introduced in the Armv8.3-A extension

• The Dot Product instruction support introduced in the Armv8.4-A extension.

• The PSTATE

Speculative Store Bypass Safe

(SSBS) bit and the speculation barriers (CSDB, SSBB,

PSSBB) instructions introduced in the Armv8.5-A extension.

The Cortex-A76 core has a

Level 1

(L1) memory system and a private, integrated

Level 2

(L2) cache. It

also includes a superscalar, variable-length, out-of-order pipeline.

The Cortex-A76 core is implemented inside the DynamIQ Shared Unit (DSU) cluster. For more

information, see the

Arm

®

DynamIQ

™

Shared Unit Technical Reference Manual

.

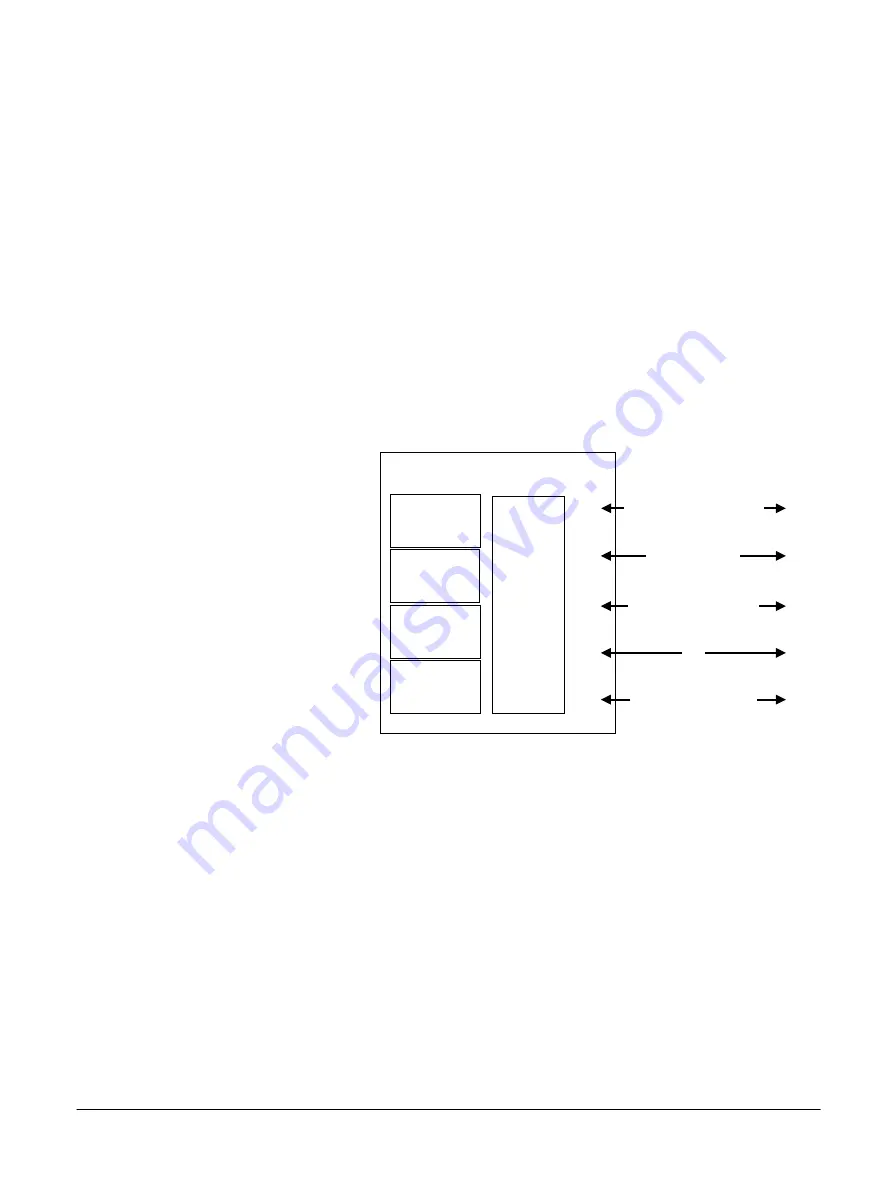

The following figure shows an example of a configuration with four Cortex-A76 cores.

External memory interface

DSU

Interrupt interface

Power management and

clock control

DFT

CoreSight infrastructure

DynamIQ™

Cluster

Core 0

Core 1

Core 2

Core 3

Figure A1-1 Example Cortex-A76 configuration

A1 Introduction

A1.1 About the core

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A1-26

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......