B2.90

SCTLR_EL1, System Control Register, EL1

The SCTLR_EL1 provides top-level control of the system, including its memory system, at EL1 and

EL0.

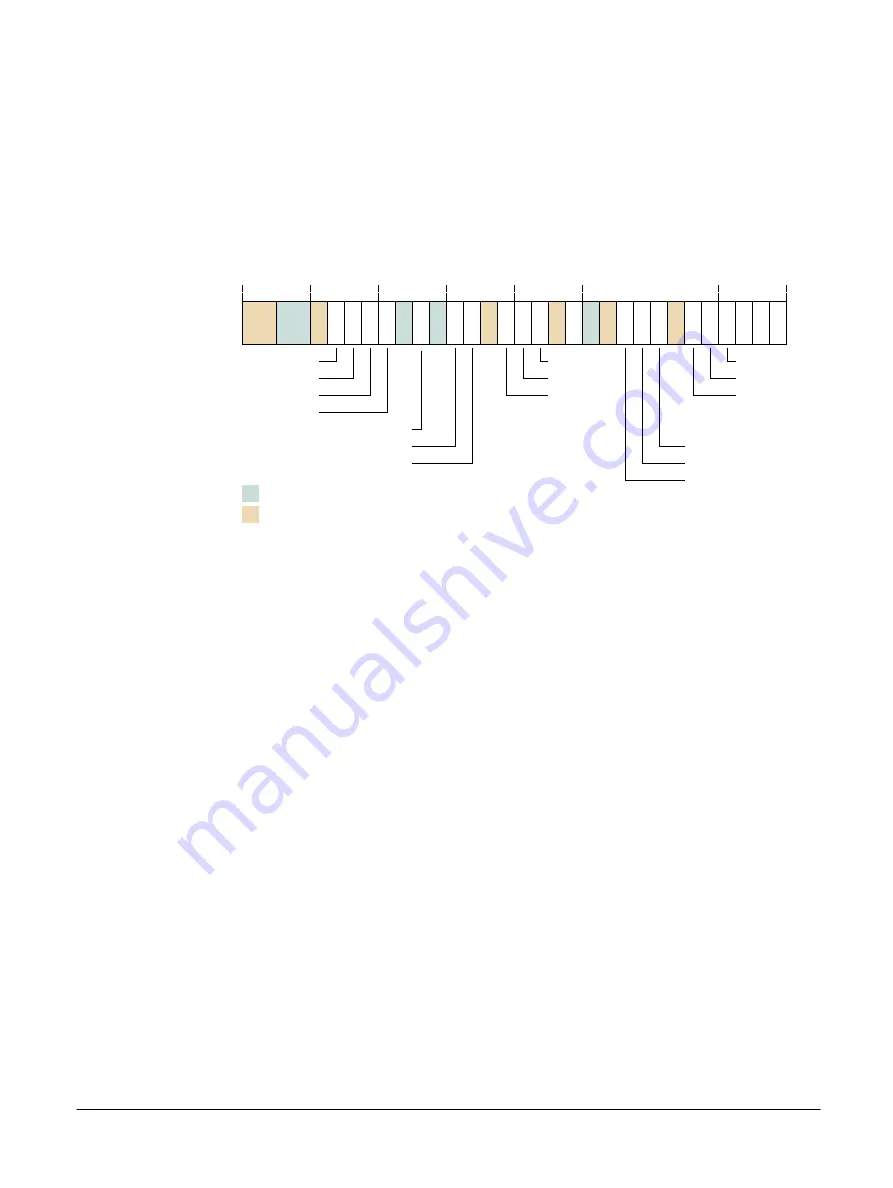

Bit field descriptions

SCTLR_EL1 is a 32-bit register, and is part of the Other system control registers functional group.

This register resets to

0x30D50838

.

31

0

M

A

C

I

SA

CP15BEN

ITD

SED

UMA

SA0

EE

DZE

nTWI

UCT

E0E

UCI

25

26

24 23

20

18

19

17 16 15

13

14

12 11 10

8

9

7 6 5

3

4

2 1

27

28

29

30

21

22

WXN

nTWE

RES

0

RES

1

SPAN

IESB

Figure B2-74 SCTLR_EL1 bit assignments

RES0, [31:30]

RES0

Reserved.

RES1, [29:28]

RES1

Reserved.

RES0, [27]

RES0

Reserved.

EE, [25]

Exception endianness. The value of this bit controls the endianness for explicit data accesses at

EL1. This value also indicates the endianness of the translation table data for translation table

lookups. The possible values of this bit are:

0

Little-endian.

1

Big-endian.

ITD, [7]

This field is

RAZ/WI

.

RES0, [6]

RES0

Reserved.

CP15BEN, [5]

CP15 barrier enable. The possible values are:

0

CP15 barrier operations disabled. Their encodings are

UNDEFINED

.

B2 AArch64 system registers

B2.90 SCTLR_EL1, System Control Register, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-273

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......