B3.4

ERR0FR, Error Record Feature Register

The ERR0FR defines which of the common architecturally defined features are implemented and, of the

implemented features, which are software programmable.

Bit field descriptions

ERR0FR is a 64-bit register, and is part of the

Reliability, Availability, Serviceability

(RAS) registers

functional group.

The register is Read Only.

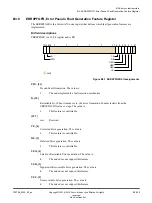

63

0

RES

0

CEC

1

2

3

4

5

6

7

8

9

10

11

12

14

15

16

CFI

UE

FI

UI

ED

RP

17

18

19

20

CEO DUI

Figure B3-3 ERR0FR bit assignments

[63:20]

RES0

Reserved.

CEO, [19:18]

Corrected Error Overwrite. The value is:

00

Counts CE if a counter is implemented and keeps the previous error status. If the

counter overflows, ERR0STATUS.OF is set to 1.

DUI, [17:16]

Error recovery interrupt for deferred errors. The value is:

00

The core does not support this feature.

RP, [15]

Repeat counter. The value is:

1

A first repeat counter and a second other counter are implemented. The repeat counter

is the same size as the primary error counter.

CEC, [14:12]

Corrected Error Counter. The value is:

010

The node implements an 8-bit standard CE counter in ERR0MISC0[39:32].

CFI, [11:10]

Fault handling interrupt for corrected errors. The value is:

10

The node implements a control for enabling fault handling interrupts on corrected

errors.

UE, [9:8]

In-band uncorrected error reporting. The value is:

01

The node implements in-band uncorrected error reporting, that is external aborts.

FI, [7:6]

B3 Error system registers

B3.4 ERR0FR, Error Record Feature Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B3-296

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......