B3.8

ERR0PFGCTLR, Error Pseudo Fault Generation Control Register

The ERR0PFGCTLR is the Cortex-A76 node register that enables controlled fault generation.

Bit field descriptions

ERR0PFGCTLR is a 32-bit read/write register.

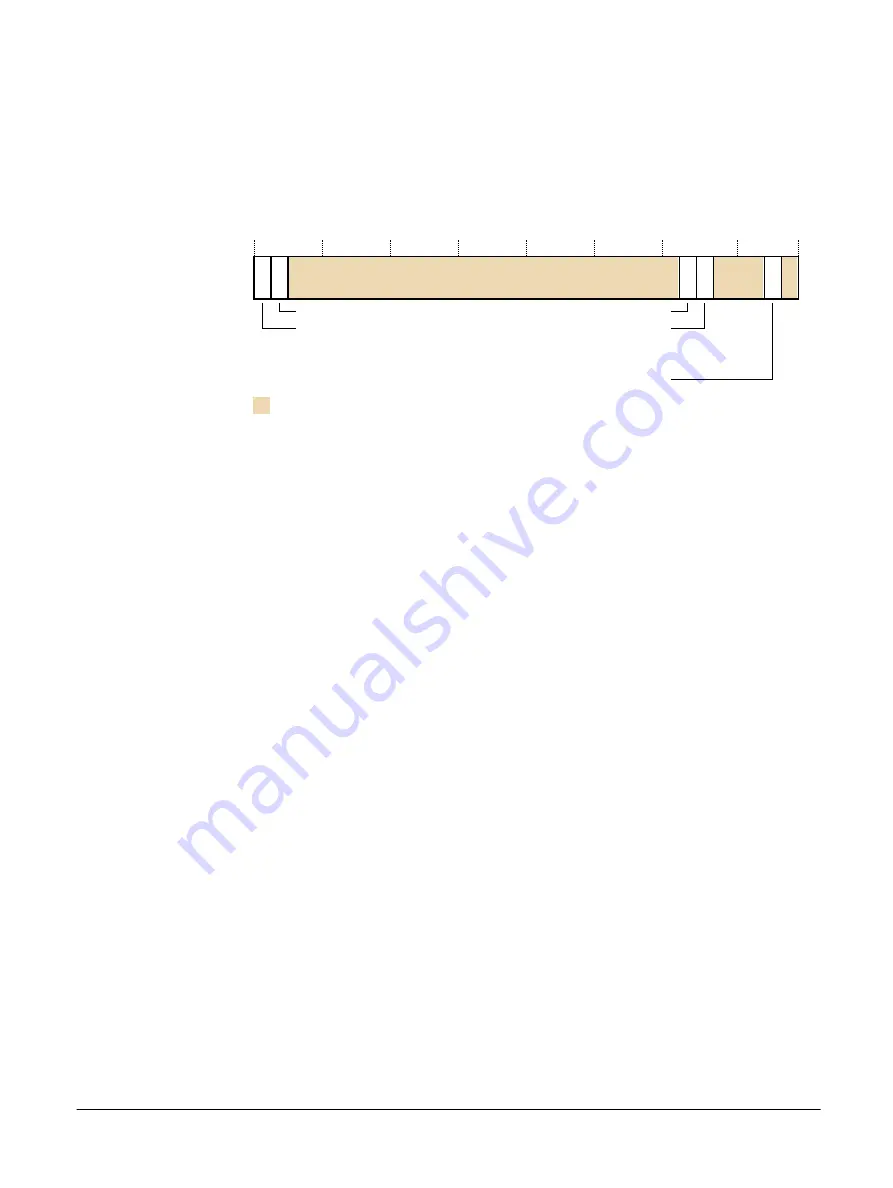

31 30

6 5 4

2

0

DE

R

CE

7

UC

1

CDNEN

29

RES

0

Figure B3-6 ERR0PFGCTLR bit assignments

CDNEN, [31]

Count down enable. This bit controls transfers from the value that is held in the

ERR0PFGCDNR into the Error Generation Counter and enables this counter to start counting

down. The possible values are:

0

The Error Generation Counter is disabled.

1

The value that is held in the ERR0PFGCDNR register is transferred into the

Error Generation Counter. The Error Generation Counter counts down.

R, [30]

Restartable bit. When it reaches 0, the Error Generation Counter restarts from the

ERR0PFGCDNR value or stops. The possible values are:

0

When it reaches 0, the counter stops.

1

When it reaches 0, the counter reloads the value that is stored in ERR0PFGCDNR

and starts counting down again.

[29:7]

Reserved,

RES0

.

CE, [6]

Corrected error generation enable. The possible values are:

0

No corrected error is generated.

1

A corrected error might be generated when the Error Generation Counter is

triggered.

DE, [5]

Deferred Error generation enable. The possible values are:

0

No deferred error is generated.

1

A deferred error might be generated when the Error Generation Counter is

triggered.

B3 Error system registers

B3.8 ERR0PFGCTLR, Error Pseudo Fault Generation Control Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B3-303

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......