B5.2

FPCR, Floating-point Control Register

The FPCR controls floating-point behavior.

Bit field descriptions

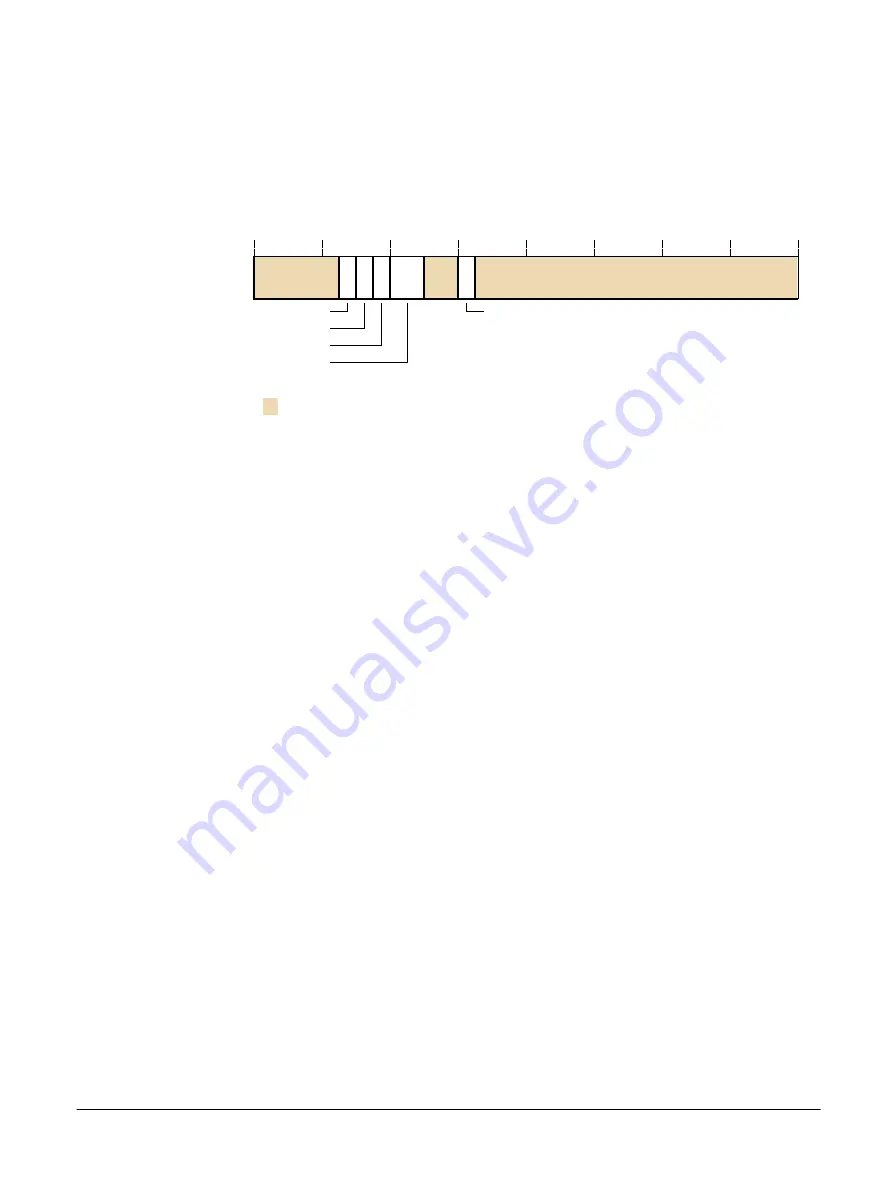

FPCR is a 32-bit register.

31

0

27 26 25 24 23 22 21

AHP

DN

FZ16

20 19 18

FZ

RMode

RES

0

Figure B5-1 FPCR bit assignments

RES0, [31:27]

RES0

Reserved.

AHP, [26]

Alternative half-precision control bit. The possible values are:

0

IEEE half-precision format selected. This is the reset value.

1

Alternative half-precision format selected.

DN, [25]

Default NaN mode control bit. The possible values are:

0

NaN operands propagate through to the output of a floating-point operation. This is the

reset value.

1

Any operation involving one or more NaNs returns the Default NaN.

FZ, [24]

Flush-to-zero mode control bit. The possible values are:

0

Flush-to-zero mode disabled. Behavior of the floating-point system is fully compliant

with the IEEE 754 standard. This is the reset value.

1

Flush-to-zero mode enabled.

RMode, [23:22]

Rounding Mode control field. The encoding of this field is:

0b00

Round to Nearest

(RN) mode. This is the reset value.

0b01

Round towards Plus Infinity

(RP) mode.

0b10

Round towards Minus Infinity

(RM) mode.

0b11

Round towards Zero

(RZ) mode.

RES0, [21:20]

RES0

Reserved.

B5 Advanced SIMD and floating-point registers

B5.2 FPCR, Floating-point Control Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B5-347

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......