D3.12

EDPIDR4, External Debug Peripheral Identification Register 4

The EDPIDR4 provides information to identify an external debug component.

Bit field descriptions

The EDPIDR4 is a 32-bit register.

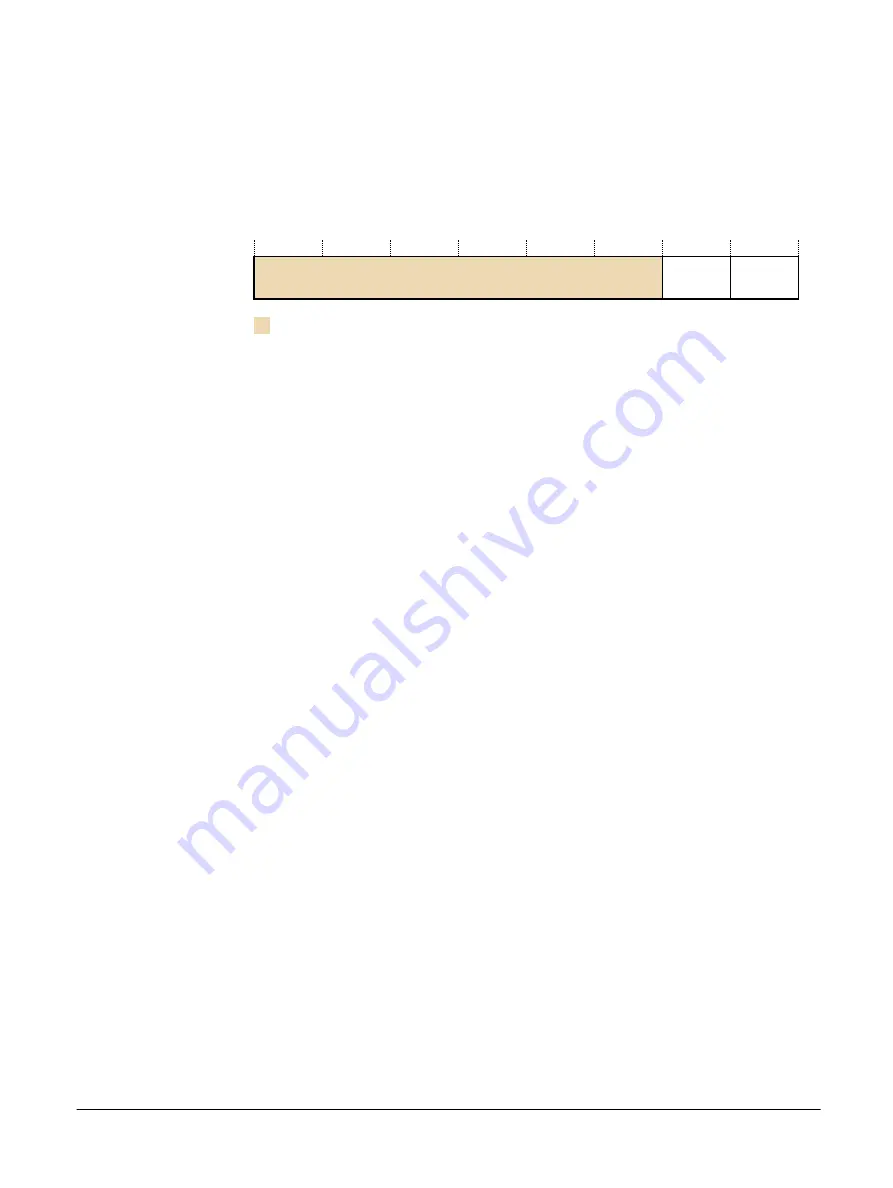

31

0

3

4

DES_2

7

8

SIZE

RES

0

Figure D3-11 EDPIDR4 bit assignments

RES0, [31:8]

RES0

Reserved.

SIZE, [7:4]

0x0

Size of the component. Log

2

the number of 4KB pages from the start of the

component to the end of the component ID registers.

DES_2, [3:0]

0x4

Arm Limited This is the least significant nibble JEP106 continuation code.

Bit fields and details not provided in this description are architecturally defined. See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

.

The EDPIDR4 can be accessed through the external debug interface, offset

0xFD0

.

D3 Memory-mapped debug registers

D3.12 EDPIDR4, External Debug Peripheral Identification Register 4

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D3-430

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......