A4.6

Core power modes

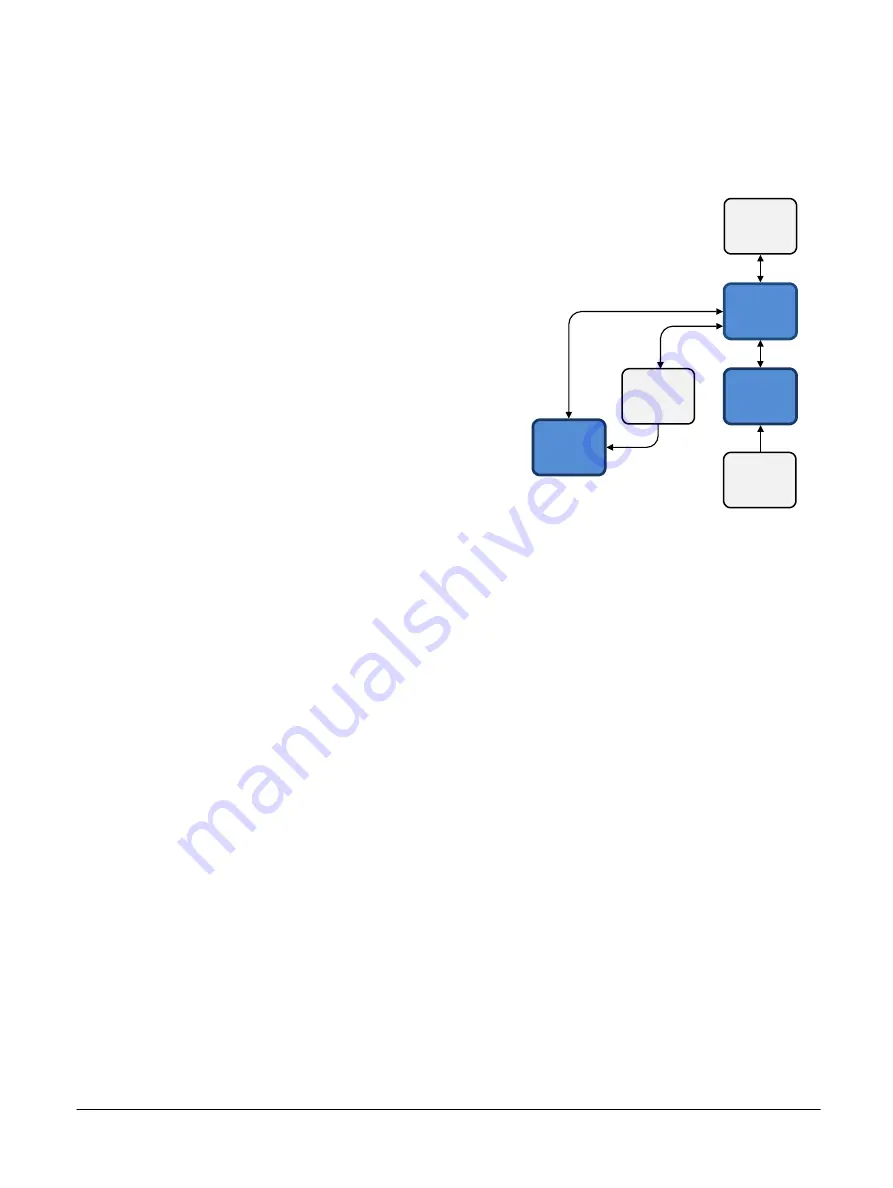

The following figure shows the supported modes for each core domain P-Channel, and the legal

transitions between them.

Off

Off

(Emulated)

Debug

Recovery

On

Dynamic

retention

From any

power mode

Figure A4-4 Cortex-A76 core power domain mode transitions

The blue modes indicate the modes the channel can be initialized into.

A4.6.1

On

In this mode, the core is on and fully operational.

The core can be initialized into the On mode. If the core does not use P-Channel, you can tie the core in

the On mode by tying

PREQ

LOW.

When a transition to the On mode completes, all caches are accessible and coherent. Other than the

normal architectural steps to enable caches, no additional software configuration is required.

When the core domain P-Channel is initialized into the On mode, either as a shortcut for entering that

mode or as a tie-off for an unused P-Channel, it is an assumed transition from the Off mode. This

includes an invalidation of any cache RAM within the core domain.

A4.6.2

Off

The Cortex-A76 core supports a full shutdown mode where power can be removed completely and no

state is retained.

The shutdown can be for either the whole cluster or just for an individual core, which allows other cores

in the cluster to continue operating.

In this mode, all core logic and RAMs are off. The domain is inoperable and all core state is lost. The L1

and L2 caches are disabled, flushed and the core is removed from coherency automatically on transition

to Off mode.

A Cold reset can reset the core in this mode.

The core P-Channel can be initialized into this mode.

An attempted debug access when the core domain is off returns an error response on the internal debug

interface indicating the core is not available.

A4 Power management

A4.6 Core power modes

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A4-53

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......