D9.26

TRCEVENTCTL0R, Event Control 0 Register

The TRCEVENTCTL0R controls the tracing of events in the trace stream. The events also drive the

external outputs from the ETM trace unit. The events are selected from the Resource Selectors.

Bit field descriptions

The TRCEVENTCTL0R is a 32-bit register.

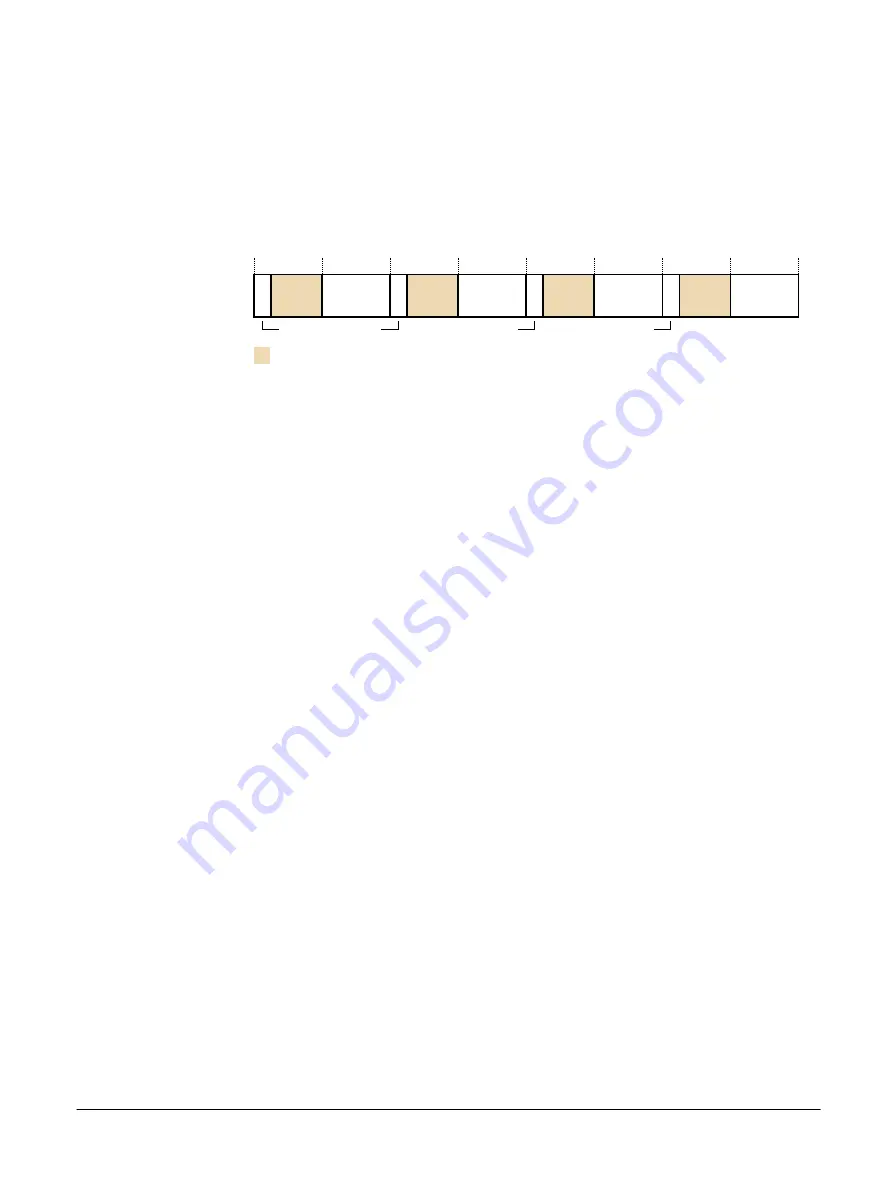

31

16 15 14

12 11

8 7

4 3

0

TYPE3

SEL1

30

28 27

24 23 22

20 19

SEL3

SEL2

TYPE2

TYPE0

TYPE1

SEL0

6

RES

0

Figure D9-24 TRCEVENTCTL0R bit assignments

TYPE3, [31]

Selects the resource type for trace event 3:

0

Single selected resource.

1

Boolean combined resource pair.

RES0, [30:28]

RES0

Reserved.

SEL3, [27:24]

Selects the resource number, based on the value of TYPE3:

When TYPE3 is 0, selects a single selected resource from 0-15 defined by bits[3:0].

When TYPE3 is 1, selects a Boolean combined resource pair from 0-7 defined by bits[2:0].

TYPE2, [23]

Selects the resource type for trace event 2:

0

Single selected resource.

1

Boolean combined resource pair.

RES0, [22:20]

RES0

Reserved.

SEL2, [19:16]

Selects the resource number, based on the value of TYPE2:

When TYPE2 is 0, selects a single selected resource from 0-15 defined by bits[3:0].

When TYPE2 is 1, selects a Boolean combined resource pair from 0-7 defined by bits[2:0].

TYPE1, [15]

Selects the resource type for trace event 1:

0

Single selected resource.

1

Boolean combined resource pair.

RES0, [14:12]

D9 ETM registers

D9.26 TRCEVENTCTL0R, Event Control 0 Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-530

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......