A4.8

Power domain states for power modes

The power domains can be controlled independently to give different combinations when powered-up

and powered-down.

However, only some powered-up and powered-down domain combinations are valid and supported. The

following information shows the supported power domain states for the Cortex-A76 core.

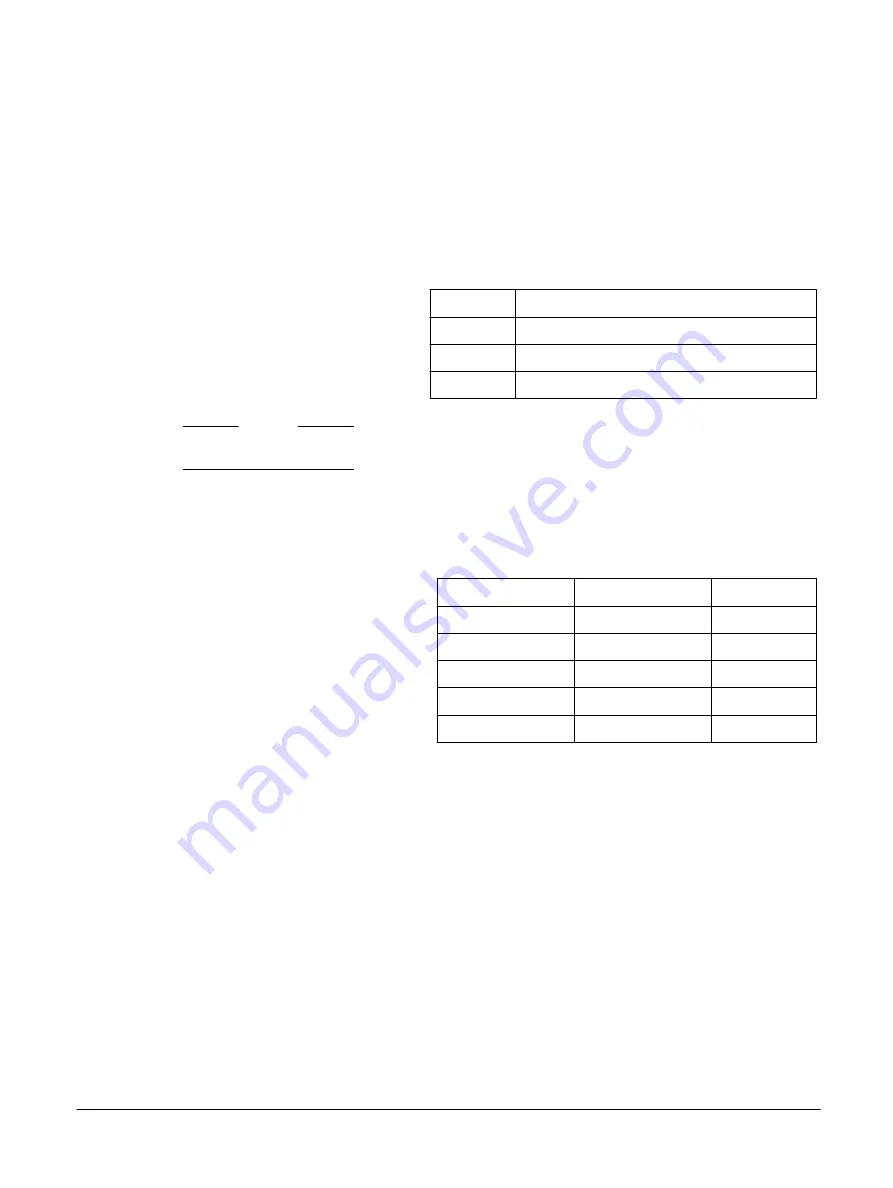

The PDCPU power domain supports the power states described in the following table.

Table A4-3 Power state description

Power state Description

Off

Core off. Power to the block is gated.

Ret

Core retention. Logic and RAM retention power only.

On

Core on. Block is active.

Caution

States that are not shown in the following tables are unsupported and must not occur.

The following table describes the power modes, and the corresponding power domain states for

individual cores. The power mode of each core is independent of all other cores in the cluster.

Table A4-4 Supported core power domain states

Power mode

Power domain state Description

Debug recovery

On

Core on.

On

On

Core on.

Core dynamic retention Ret

Core in retention.

Off (emulated)

On

Core on.

Off

Off

Core off.

Deviating from the legal power modes can lead to

UNPREDICTABLE

results. You must comply with the

dynamic power management and powerup and powerdown sequences described in the following

sections.

A4 Power management

A4.8 Power domain states for power modes

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A4-57

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......