D9.72

TRCVICTLR, ViewInst Main Control Register

The TRCVICTLR controls instruction trace filtering.

Bit field descriptions

The TRCVICTLR is a 32-bit register.

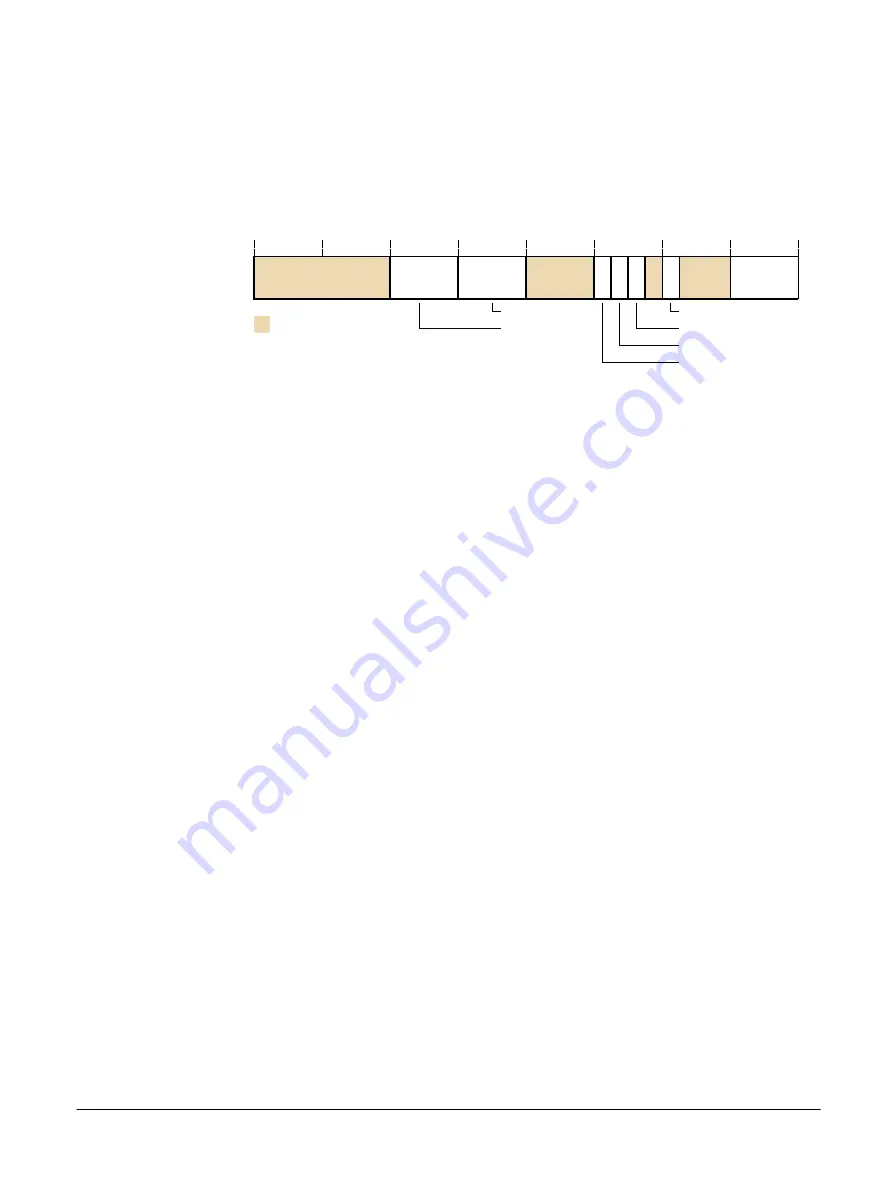

31

0

7

8

9

10

11

15

12

16

19

20

23

24

SSSTATUS

TRCRESET

TRCERR

EXLEVEL_S

EXLEVEL_NS

6

3

4

SEL

TYPE

RES

0

Figure D9-69 TRCVICTLR bit assignments

RES0, [31:24]

RES0

Reserved.

EXLEVEL_NS, [23:20]

In Non-secure state, each bit controls whether instruction tracing is enabled for the

corresponding exception level:

0

Trace unit generates instruction trace, in Non-secure state, for exception level

n

.

1

Trace unit does not generate instruction trace, in Non-secure state, for exception level

n

.

The exception levels are:

Bit[20]

Exception level 0.

Bit[21]

Exception level 1.

Bit[22]

Exception level 2.

Bit[23]

RAZ/WI. Instruction tracing is not implemented for exception level 3.

EXLEVEL_S, [19:16]

In Secure state, each bit controls whether instruction tracing is enabled for the corresponding

exception level:

0

Trace unit generates instruction trace, in Secure state, for exception level

n

.

1

Trace unit does not generate instruction trace, in Secure state, for exception level

n

.

The exception levels are:

Bit[16]

Exception level 0.

Bit[17]

Exception level 1.

Bit[18]

RAZ/WI. Instruction tracing is not implemented for exception level 2.

Bit[19]

Exception level 3.

RES0, [15:12]

RES0

Reserved.

TRCERR, [11]

D9 ETM registers

D9.72 TRCVICTLR, ViewInst Main Control Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-583

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......