A6.6

Direct access to internal memory

The Cortex-A76 core provides a mechanism to read the internal memory that is used by the L1 caches,

L2 cache, and TLB structures through implementation defined system registers. This functionality can be

useful when debugging software or hardware issues.

When the core executes in AArch64 state, there are six read-only registers that are used to access the

contents of the internal memory. The internal memory is selected by programming the implementation-

defined RAMINDEX register (using SYS #6, c15, c0, #0 instruction). These operations are available

only in EL3. In all other modes, executing these instructions results in an Undefined Instruction

exception. The data is read from read-only registers as shown in the following table.

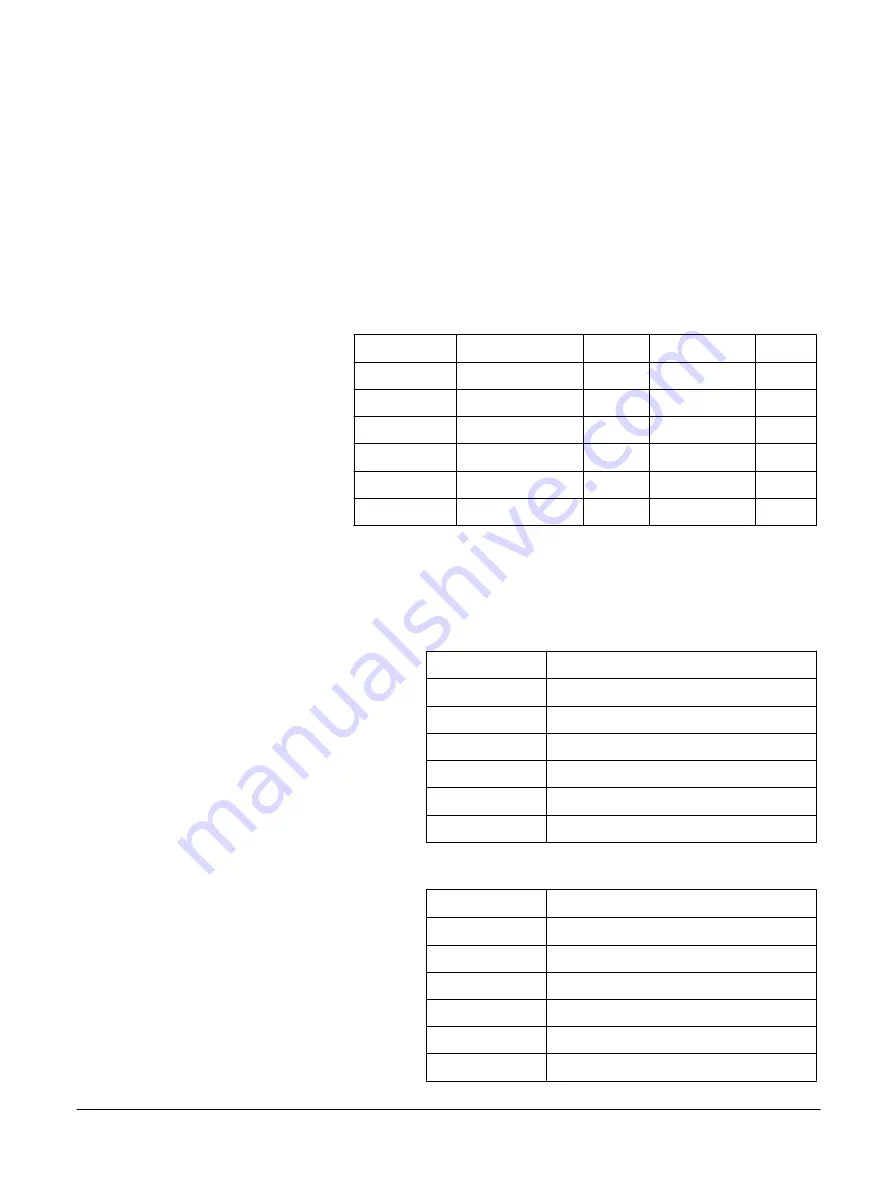

Table A6-1 AArch64 registers used to access internal memory

Register name Function

Access

Operation

Rd Data

IDATA0_EL3

Instruction Register 0 Read-only

S3_6_c15_c0_0

Data

IDATA1_EL3

Instruction Register 1 Read-only

S3_6_c15_c0_1

Data

IDATA2_EL3

Instruction Register 2 Read-only

S3_6_c15_c0_2

Data

DDATA0_EL3

Data Register 0

Read-only

S3_6_c15_c1_0

Data

DDATA1_EL3

Data Register 1

Read-only

S3_6_c15_c1_1

Data

DDATA2_EL3

Data Register 2

Read-only

S3_6_c15_c1_2

Data

A6.6.1

Encoding for L1 instruction cache tag, L1 instruction cache data, L1 BTB, L1 GHB, L1 TLB

instruction, and BPIQ

The following tables show the encoding required to select a given cache line.

Table A6-2 L1 instruction cache tag location encoding

Bit fields of Rd

Description

[31:24]

RAMID =

0x00

[23:20]

Reserved

[19:18]

Way

[17:14]

Reserved

[13:6]

Index [13:6]

[5:0]

Reserved

Table A6-3 L1 instruction cache data location encoding

Bit fields of Rd

Description

[31:24]

RAMID =

0x01

[23:20]

Reserved

[19:18]

Way

[17:14]

Reserved

[13:3]

Index [13:3]

[2:0]

Reserved

A6 Level 1 memory system

A6.6 Direct access to internal memory

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A6-80

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......