Nested Vectored Interrupt Controller

8-18

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

Table 8-13 describes the bit assignments of the Interrupt Priority Registers, where n

specifies the number of interrupts and is greater than 0 and less than or equal to 240.

CPU ID Base Register

Read the CPU ID Base Register to determine:

•

the ID number of the processor core

•

the version number of the processor core

•

the implementation details of the processor core.

The register address, access type, and Reset state are:

Address

0xE000ED00

Access

Read-only

Reset state

0x412FC230

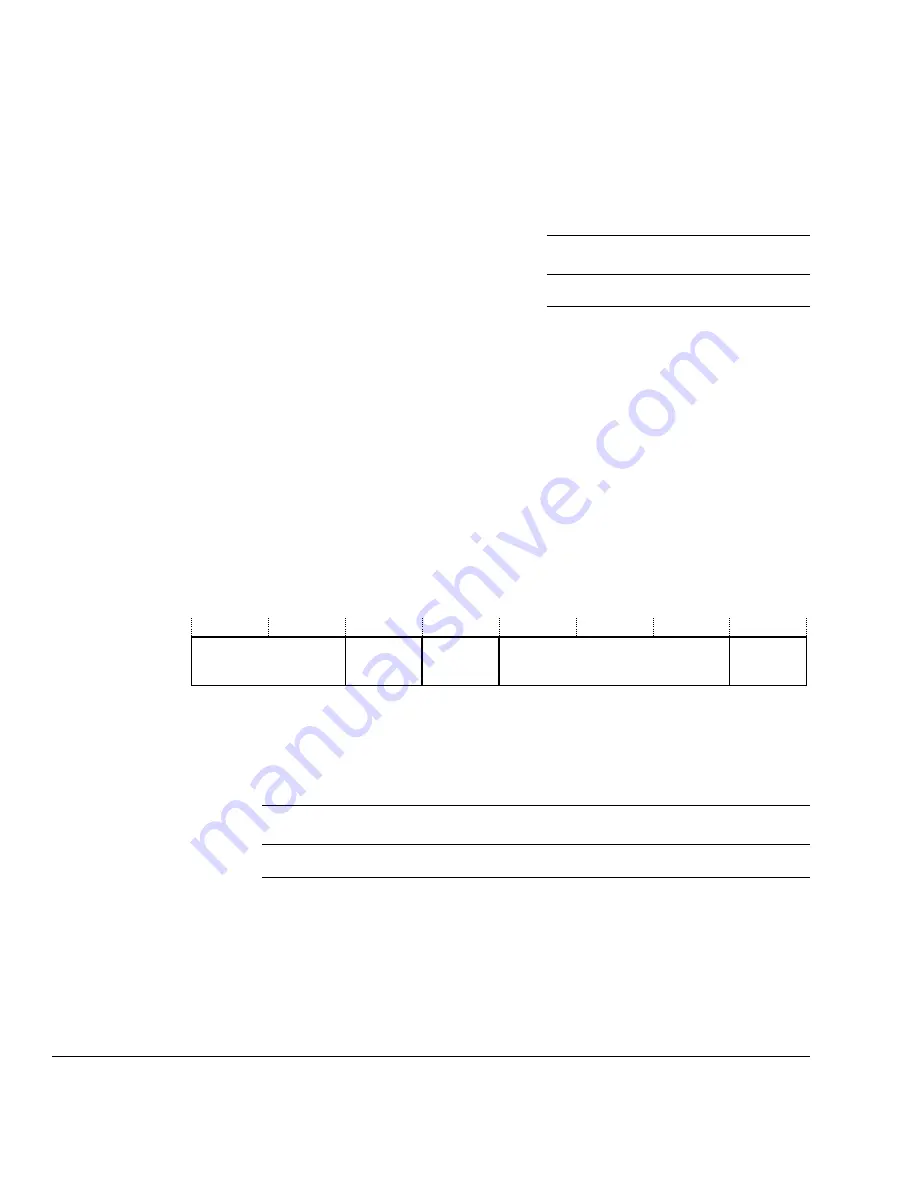

Figure 8-8 shows the bit assignments of the CPUID Base Register.

Figure 8-8 CPUID Base Register bit assignments

Table 8-14 describes the bit assignments of the CPUID Base Register.

Table 8-13 Interrupt Priority Registers 0-31 bit assignments

Bits

Field

Function

[7:0]

PRI_

n

Priority of interrupt

n

31

16 15

4 3

0

IMPLEMENTER

REVISION

PARTNO

24 23

20 19

VARIANT

Constant

Table 8-14 CPUID Base Register bit assignments

Bits

Field

Function

[31:24]

IMPLEMENTER

Implementer code. ARM is

0x41

[23:20]

VARIANT

Implementation defined variant number.