Nested Vectored Interrupt Controller

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

8-19

Unrestricted Access

Non-Confidential

Interrupt Control State Register

Use the Interrupt Control State Register to:

•

set a pending

Non-Maskable Interrupt

(NMI)

•

set or clear a pending SVC

•

set or clear a pending SysTick

•

check for pending exceptions

•

check the vector number of the highest priority pended exception

•

check the vector number of the active exception.

The register address, access type, and Reset state are:

Address

0xE000ED04

Access

Read/write or read-only

Reset state

0x00000000

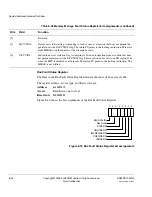

Figure 8-9 on page 8-20 shows the bit assignments of the Interrupt Control State

Register.

[19:16]

Constant

Reads as

0xF

[15:4]

PARTNO

Number of processor within family:

[11:10] b11 = Cortex family

[9:8] b00 = version

[7:6] b00 = reserved

[5:4] b10 = M (v7-M)

[3:0] X = family member. Cortex-M3 family is b0011.

[3:0]

REVISION

Implementation defined revision number.

Table 8-14 CPUID Base Register bit assignments (continued)

Bits

Field

Function