Nested Vectored Interrupt Controller

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

8-21

Unrestricted Access

Non-Confidential

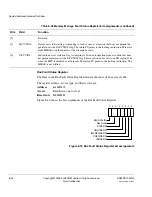

Vector Table Offset Register

Use the Vector Table Offset Register to determine:

•

if the vector table is in RAM or code memory

•

the vector table offset.

The register address, access type, and Reset state are:

Address

0xE000ED08

Access

Read/write

Reset state

0x00000000

Figure 8-10 on page 8-22 shows the bit assignments of the Vector Table Offset Register.

[24]

-

-

Reserved

[23]

ISRPREEMPT

Read-only

You must only use this at debug time. It indicates that a pending interrupt

becomes active in the next running cycle. If C_MASKINTS is clear in the

Debug Halting Control and Status Register, the interrupt is serviced.

[22]

ISRPENDING

Read-only

Interrupt pending flag. Excludes NMI and Faults:

1 = interrupt pending

0 = interrupt not pending.

[21:12]

VECTPENDING

Read-only

Pending ISR number field. VECTPENDING contains the interrupt number

of the highest priority pending ISR.

[11]

RETTOBASE

Read-only

This bit is 1 when the set of all active exceptions minus the

IPSR_current_exception yields the empty set.

[10]

-

-

Reserved.

[9]

-

-

Reserved

[8:0]

VECTACTIVE

Read-only

Active ISR number field. VECTACTIVE contains the interrupt number of

the currently running ISR, including NMI and Hard Fault. A shared handler

can use VECTACTIVE to determine which interrupt invoked it. You can

subtract 16 from the VECTACTIVE field to index into the Interrupt

Clear/Set Enable, Interrupt Clear Pending/SetPending and Interrupt Priority

Registers.

INTISR[0]

has vector number 16.

Reset clears the VECTACTIVE field.

Table 8-15 Interrupt Control State Register bit assignments (continued)

Bits

Field

Type

Function