Nested Vectored Interrupt Controller

8-22

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

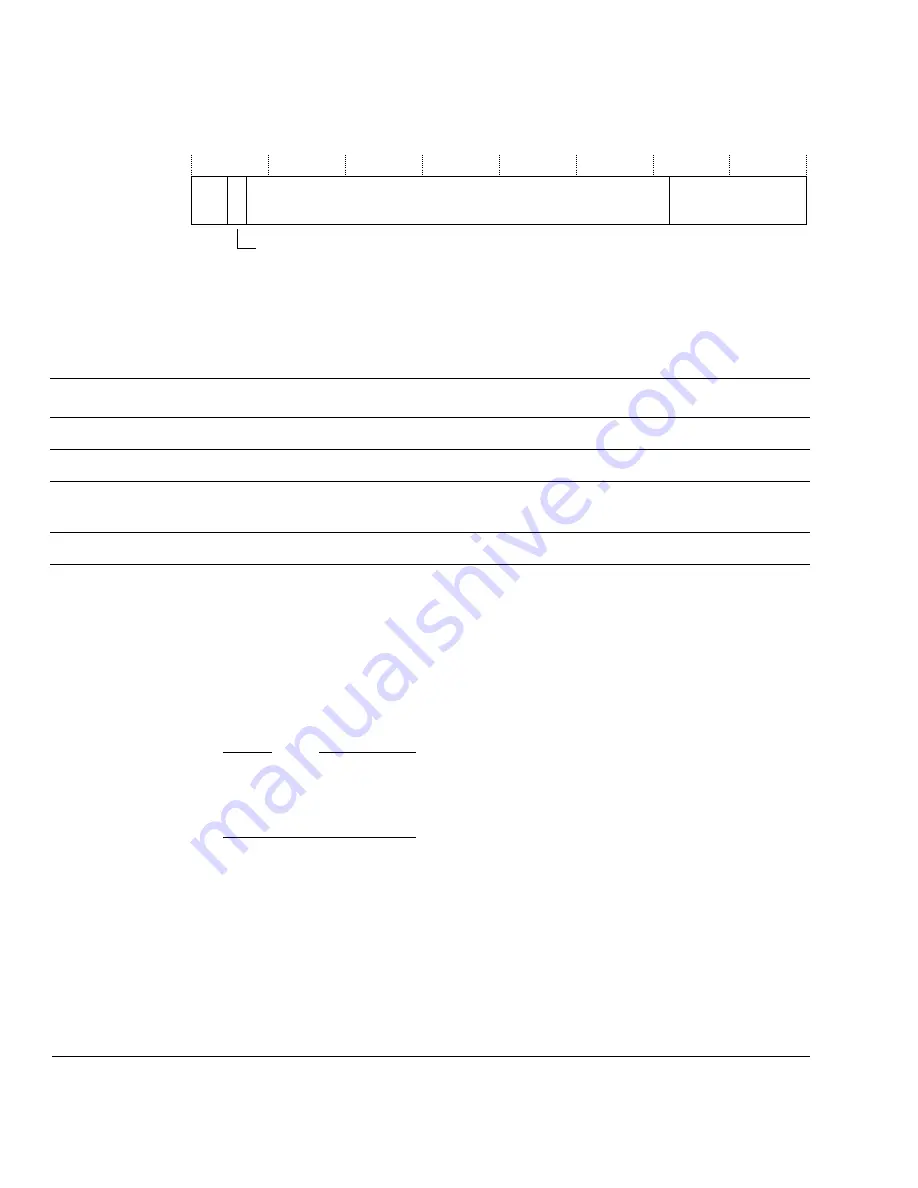

Figure 8-10 Vector Table Offset Register bit assignments

Table 8-16 describes the bit assignments of the Vector Table Offset Register.

The Vector Table Offset Register positions the vector table in CODE or SRAM space.

The default, on reset, is 0 (CODE space). When setting a position, the offset must be

aligned based on the number of exceptions in the table. This means that the minimum

alignment is 32 words that you can use for up to 16 interrupts. For more interrupts, you

must adjust the alignment by rounding up to the next power of two. For example, if you

require 21 interrupts, the alignment must be on a 64-word boundary because table size

is 37 words, next power of two is 64.

Note

Table alignment requirements mean that bits [6:0] of the table offset are always zero.

TBLBASE and TBLOFF are combined with 7'b0000000 to construct the complete

vector table base offset value.

Application Interrupt and Reset Control Register

Use the Application Interrupt and Reset Control Register to:

•

determine data endianness

•

clear all active state information for debug or to recover from a hard failure

•

execute a system reset

•

alter the priority grouping position (binary point).

31

0

7 6

Reserved

TBLOFF

28

TBLBASE

29

30

Res

Table 8-16 Vector Table Offset Register bit assignments

Bits

Field

Function

[31:30]

-

Reserved, RAZ/WI

[29]

TBLBASE

Table base is in Code (0) or RAM (1)

[28:7]

TBLOFF

Vector table base offset field. Contains the offset of the table base from the bottom of the SRAM

or CODE space.

[6:0]

-

Reserved, RAZ/WI