Nested Vectored Interrupt Controller

8-24

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

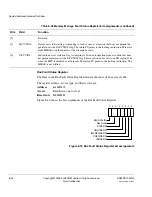

PRIGROUP 0

1

2

3

4

5

6

7

Split of pre-emption priority from subpriority

7.1 indicates seven bits of pre-emption priority, one bit of subpriority

6.2 indicates six bits of pre-emption priority, two bits of subpriority

5.3 indicates five bits of pre-emption priority, three bits of subpriority

4.4 indicates four bits of pre-emption priority, four bits of subpriority

3.5 indicates three bits of pre-emption priority, five bits of subpriority

2.6 indicates two bits of pre-emption priority, six bits of subpriority

1.7 indicates one bit of pre-emption priority, seven bits of subpriority

0.8 indicates no pre-emption priority, eight bits of subpriority.

PRIGROUP field is a binary point position indicator for creating subpriorities for

exceptions that share the same pre-emption level. It divides the PRI_

n

field in the

Interrupt Priority Register into a pre-emption level and a subpriority level. The binary

point is a left-of value. This means that the PRIGROUP value represents a point starting

at the left of the

Least Significant Bit

(LSB). This is bit [0] of 7:0.

The lowest value might not be 0 depending on the number of bits allocated for priorities,

and implementation choices.

[7:3]

- Reserved.

[2]

SYSRESETREQ

Causes a signal to be asserted to the outer system that indicates a reset is requested.

Intended to force a large system reset of all major components except for debug. Setting

this bit does not prevent Halting Debug from running.

[1]

VECTCLRACTIVE

Clear active vector bit:

1 = clear all state information for active NMI, fault, and interrupts

0 = do not clear.

It is the responsibility of the application to reinitialize the stack.

The VECTCLRACTIVE bit is for returning to a known state during debug. The

VECTCLRACTIVE bit self-clears.

IPSR is not cleared by this operation. So, if used by an application, it must only be used

at the base level of activation, or within a system handler whose active bit can be set.

[0]

VECTRESET

System Reset bit. Resets the system, with the exception of debug components:

1 = reset system

0 = do not reset system.

The VECTRESET bit self-clears. Reset clears the VECTRESET bit.

For debugging, only write this bit when the core is halted.

Table 8-17 Application Interrupt and Reset Control Register bit assignments (continued)

Bits

Field

Function