Nested Vectored Interrupt Controller

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

8-27

Unrestricted Access

Non-Confidential

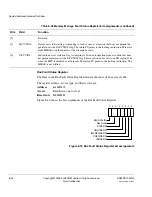

Figure 8-13 shows the bit assignments of the Configuration Control Register.

Figure 8-13 Configuration Control Register bit assignments

Table 8-19 describes the bit assignments of the Configuration Control Register.

31

0

3 2 1

Reserved

DIV_0_TRP

Reserved

UNALIGN_TRP

4

NONBASETHRDENA

USERSETMPEND

8

BFHFNMIGN

5

7

Res

9

STKALIGN

10

Table 8-19 Configuration Control Register bit assignments

Bits

Field

Function

[31:10]

_

Reserved.

[9]

STKALIGN

1 = on exception entry, the SP used prior to the exception is adjusted to be 8-byte

aligned and the context to restore it is saved. The SP is restored on the associated

exception return.

0 = only 4-byte alignment is guaranteed for the SP used prior to the exception on

exception entry.

[8]

BFHFNMIGN

When enabled, this causes handlers running at priority -1 and -2 (Hard Fault, NMI,

and FAULTMASK escalated handlers) to ignore Data Bus faults caused by load

and store instructions. When disabled, these bus faults cause a lock-up. You must

only use this enable with extreme caution. All data bus faults are ignored – you

must only use it when the handler and its data are in absolutely safe memory. Its

normal use is to probe system devices and bridges to detect control path problems

and fix them.

[7:5]

-

Reserved.

[4]

DIV_0_TRP

Trap on Divide by 0. This enables faulting/halting when an attempt is made to

divide by 0. The relevant Usage Fault Status Register bit is DIVBYZERO, see

Usage Fault Status Register

on page 8-35.