Nested Vectored Interrupt Controller

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

8-37

Unrestricted Access

Non-Confidential

Note

The fault bits are additive if more than one fault occurs before this register is cleared.

Hard Fault Status Register

Use the

Hard Fault Status Register

(HFSR) to obtain information about events that

activate the Hard Fault handler.

The register address, access type, and Reset state are:

Address

0xE000ED2C

Access

Read/write-one-to-clear

Reset state

0x00000000

The HFSR is a write-clear register. This means that writing a 1 to a bit clears that bit.

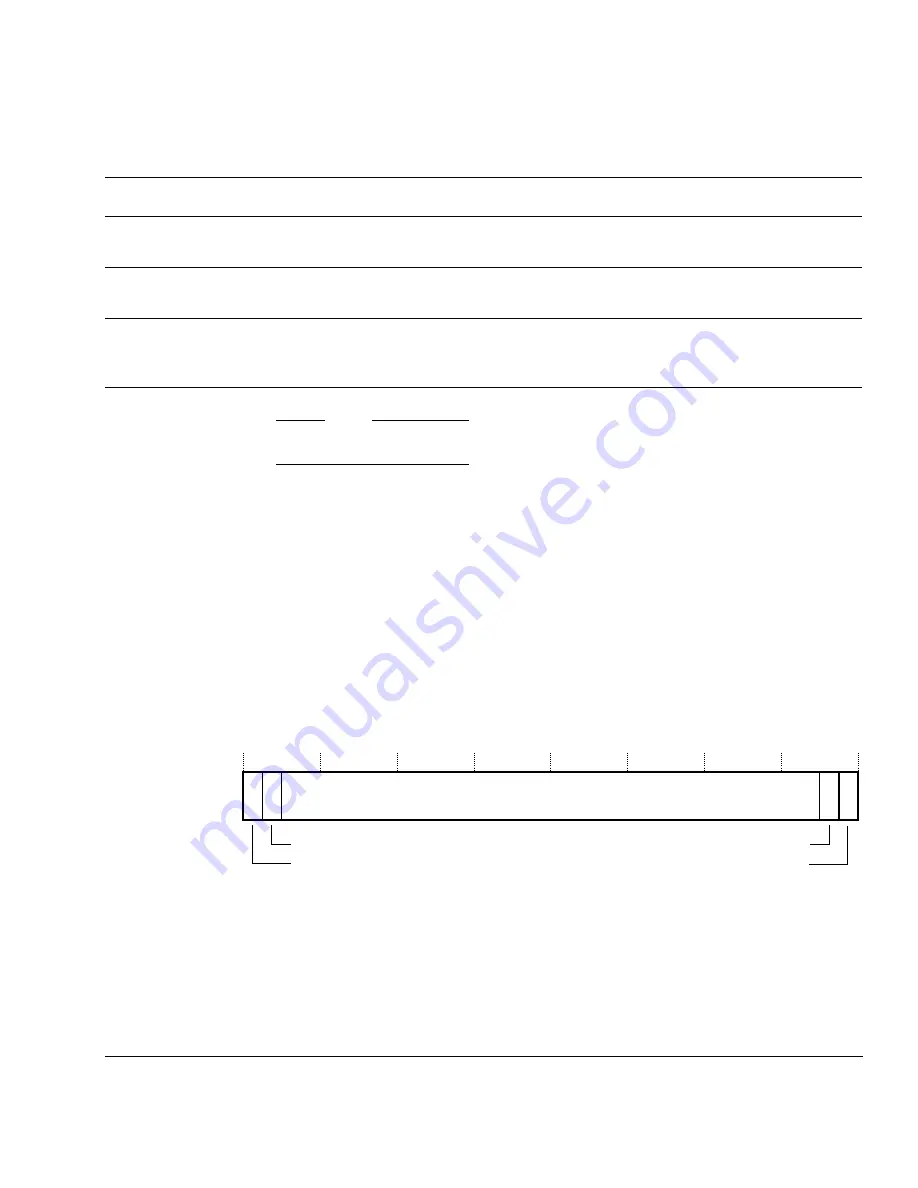

Figure 8-20 shows the bit assignments of the Hard Fault Status Register.

Figure 8-20 Hard Fault Status Register bit assignments

[2]

INVPC

Attempt to load EXC_RETURN into PC illegally. Invalid instruction, invalid context, invalid

value. The return PC points to the instruction that tried to set the PC.

[1]

INVSTATE

Invalid combination of EPSR and instruction, for reasons other than UNDEFINED

instruction. Return PC points to faulting instruction, with the invalid state.

[0]

UNDEFINSTR

The UNDEFINSTR flag is set when the processor attempts to execute an undefined

instruction. This is an instruction that the processor cannot decode. The return PC points to

the undefined instruction.

Table 8-24 Usage Fault Status Register bit assignments (continued)

Bits

Field

Function

31 30

2 1 0

Reserved

29

DEBUGEVT

FORCED

VECTTBL

Reserved