System Debug

11-22

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

Table 11-11 describes the bit assignments of the DWT Sleep Count Register.

Note

SLEEPCNT is clocked using

FCLK

. It is possible that the frequency of

FCLK

might

be reduced while the processor is sleeping to minimize power consumption. This means

that sleep duration must be calculated with the frequency of

FCLK

during sleep.

DWT LSU Count Register

Use the DWT LSU Count Register to count the total number of cycles during which the

processor is processing an LSU operation beyond the first cycle.

The register address, access type, and Reset state are:

Address

0xE0001014

Access

Read/write

Reset state

-

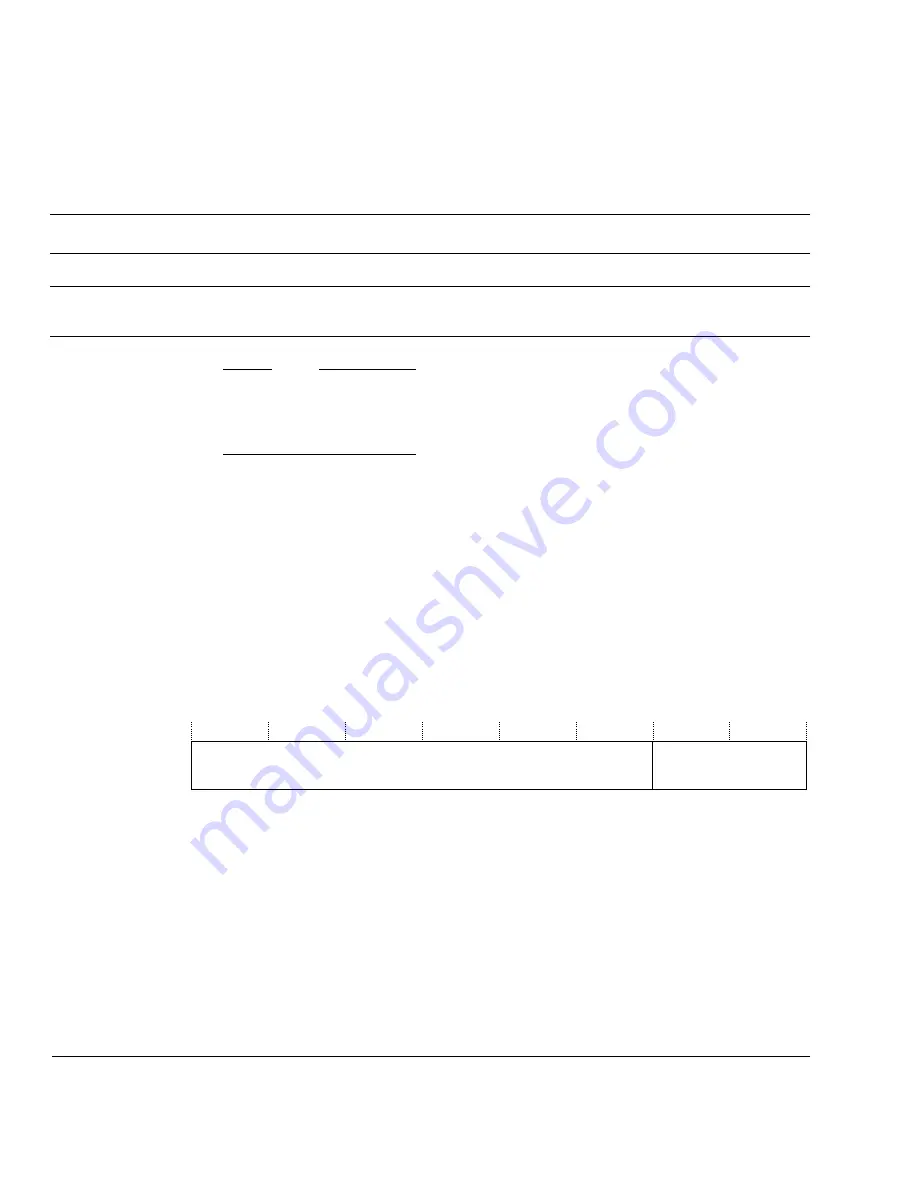

Figure 11-9 describes the bit assignments of the DWT LSU Count Register.

Figure 11-9 DWT LSU Count Register bit assignments

Table 11-11 DWT Sleep Count Register bit assignments

Bits

Field

Function

[31:8]

-

Reserved.

[7:0]

SLEEPCNT

Sleep counter. Counts the number of cycles during which the processor is sleeping. An event is

emitted on counter overflow (every 256 cycles). This counter initializes to 0 when enabled.

Reserved

31

8 7

0

LSUCNT