System Debug

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

11-41

Unrestricted Access

Non-Confidential

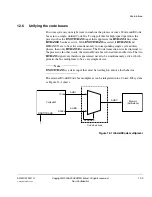

Figure 11-19 AHB-AP Control and Status Word Register

Table 11-29 describes the bit assignments of the AHB-AP Control and Status Word

Register.

11

8

31

29 28

26

30

12

7 6 5 4 3 2

0

MODE

Reserved

SIZE

25 24

TransInProg

DbgStatus

AddrInc

Hprot1

MasterType

Reserved

Reserved

Reserved

Table 11-29 AHB-AP Control and Status Word Register bit assignments

Bits

Field

Function

[31:30]

-

Reserved. Read as 0b00.

[29]

MasterType

a

0 = core.

1 = debug.

It cannot be changed if transaction is outstanding. Debugger must first check TransinProg.

Reset value = 0b1.

If the

FIXHMASTERTYPE

input signal is set to 1 then this register has no affect on the

master value indicated by the transaction. It is always marked as the debugger.

[28:26]

-

Reserved, 0b000.

[25]

Hprot1

User/Privilege control - HPROT[1].

Reset value = 0b1.

[24]

-

Reserved, 0b1.

[23:12]

-

Reserved,

0x000

.

[11:8]

Mode

Mode of operation bits:

b0000 = normal download/upload mode

b0001-b1111 are reserved.

Reset value = 0b0000.

[7]

TransINProg

Transfer in progress. This field indicates if a transfer is in progress on the APB master port.

[6] DbgStatus

Indicates

the

status

of the DAPEN port. If DbgStatus is LOW, no AHB transfers carried out.

1 = AHB transfers permitted.

0 = AHB transfers not permitted.