Bus Interface

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

12-11

Unrestricted Access

Non-Confidential

12.8

Access alignment

The processor supports unaligned data accesses using the ARMv6 model. The DCode

and System bus interfaces contain logic that converts unaligned accesses to aligned

accesses.

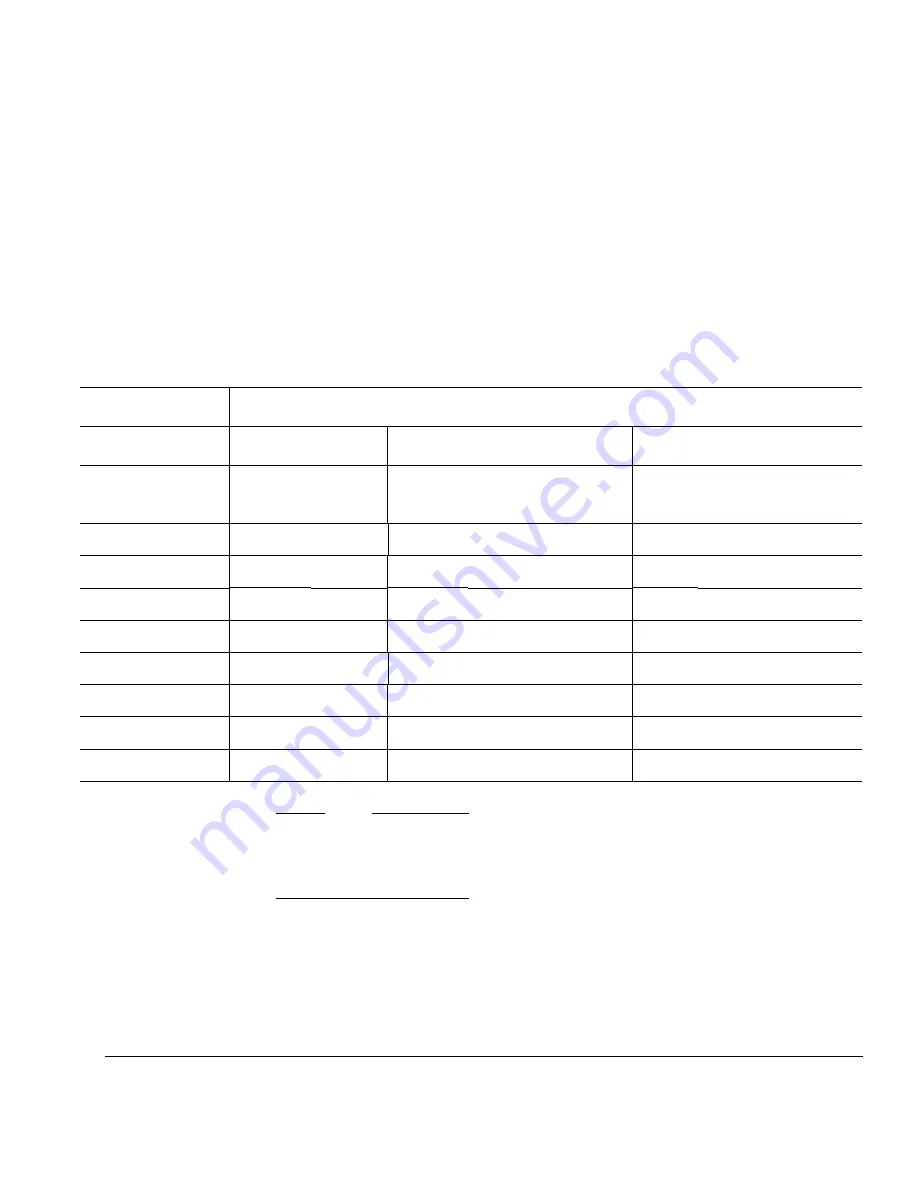

The unaligned data accesses are described in Table 12-2. The table shows the unaligned

access in the first column, with the remaining columns showing what the access is

converted into. Depending on the size and alignment of the unaligned access, it is

converted into two or three aligned accesses.

Note

Unaligned accesses that cross into the bit-band alias region are not treated as bit-band

requests, and the access is not remapped to the bit-band region. Instead, they are treated

as a halfword or byte access to the bit-band alias region.

Table 12-2 Bus mapper unaligned accesses

Unaligned access

Aligned access

Cycle 1

Cycle 2

Cycle 3

Size

ADDR

[1:0]

HSIZE

HADDR

[1:0]

HSIZE

HADDR[1:0]

HSIZE

HADDR[1:0]

Halfword

00

Halfword

00

-

-

-

-

Halfword

01

Byte

01

Byte

10

-

-

Halfword

10

Halfword

10

-

-

-

-

Halfword

11

Byte

11

Byte

{(Addr+4)[31:2],2b00}

-

-

Word

00

Word

00

-

-

-

-

Word

01

Byte

01

Halfword

10

Byte

{(Addr+4)[31:2],2b00}

Word

10

Halfword

10

Halfword

{(Addr+4)[31:2],2b00}

-

-

Word

11

Byte

11

Halfword

{(Addr+4)[31:2],2b00}

Byte

{(Addr+4)[31:2],2b10}