Introduction

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

1-3

Unrestricted Access

Non-Confidential

—

Sub Region Disable

(SRD), enabling efficient use of memory regions.

—

You can enable a background region that implements the default memory

map attributes.

•

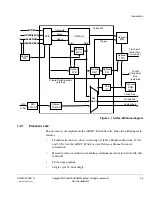

Bus interfaces:

—

Advanced High-performance Bus-Lite

(AHB-Lite) ICode, DCode and

System bus interfaces.

—

Private Peripheral Bus

(PPB) based on

Advanced Peripheral Bus

(APB)

interface.

—

Bit band support that includes atomic bit band write and read operations.

—

Memory access alignment.

—

Write buffer for buffering of write data.

—

Exclusive access transfers for multiprocessor systems.

•

Low-cost debug solution that features:

—

Debug access to all memory and registers in the system, including access to

memory mapped devices, access to internal core registers when the core is

halted, and access to debug control registers even while

SYSRESETn

is

asserted.

—

Serial Wire Debug Port

(SW-DP) or

Serial Wire JTAG Debug Port

(SWJ-DP) debug access, or both.

—

Flash Patch and Breakpoint

(FPB) unit for implementing breakpoints and

code patches.

—

Data Watchpoint and Trace

(DWT) unit for implementing watchpoints,

data tracing, and system profiling.

—

Instrumentation Trace Macrocell

(ITM) for support of printf style

debugging.

—

Trace Port Interface Unit

(TPIU) for bridging to a

Trace Port Analyzer

(TPA).

—

Optional

Embedded Trace Macrocell

(ETM) for instruction trace.