Introduction

ARM DDI 0337G

Copyright © 2005-2008 ARM Limited. All rights reserved.

1-9

Unrestricted Access

Non-Confidential

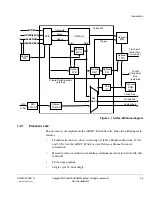

The ITM provides the following sources of trace information:

•

Software trace. Software can write directly to ITM stimulus registers. This causes

packets to be emitted.

•

Hardware trace. These packets are generated by the DWT, and emitted by the

ITM.

•

Time stamping. Timestamps are emitted relative to packets.

Chapter 11

System Debug

describes the ITM.

1.2.7

MPU

You can configure the implementation to include an MPU to provide memory

protection. The MPU checks access permissions and memory attributes. It contains

eight regions, and an optional background region that implements the default memory

map attributes.

Chapter 9

Memory Protection Unit

describes the MPU.

1.2.8

ETM

You can configure the system at implementation to include an ETM. This is a low-cost

trace macrocell that supports instruction trace only.

Chapter 14

Embedded Trace Macrocell

describes the ETM.

1.2.9

AHB-AP

You can configure the implementation to include an AHB-AP.

AHB-AP

on page 11-39 describes the AHB-AP.

1.2.10

AHB Trace Macrocell interface

You can configure the system at implementation to include an

AHB Trace Macrocell

(HTM) interface. If you do not enable this option at the time of implementation, the

HTM interface does not function because the required logic is not included.

1.2.11

TPIU

You can configure the system at implementation to include an TPIU. The TPIU acts as

a bridge between the Cortex-M3 trace data from the ITM, an ETM if present, and an

off-chip Trace Port Analyzer.