Programmer’s Model

2-8

Copyright © 2005-2008 ARM Limited. All rights reserved.

ARM DDI 0337G

Non-Confidential

Unrestricted Access

Note

Because the ICI field and the IT field overlap, load or store multiples within an If-Then

block cannot be interrupt-continued.

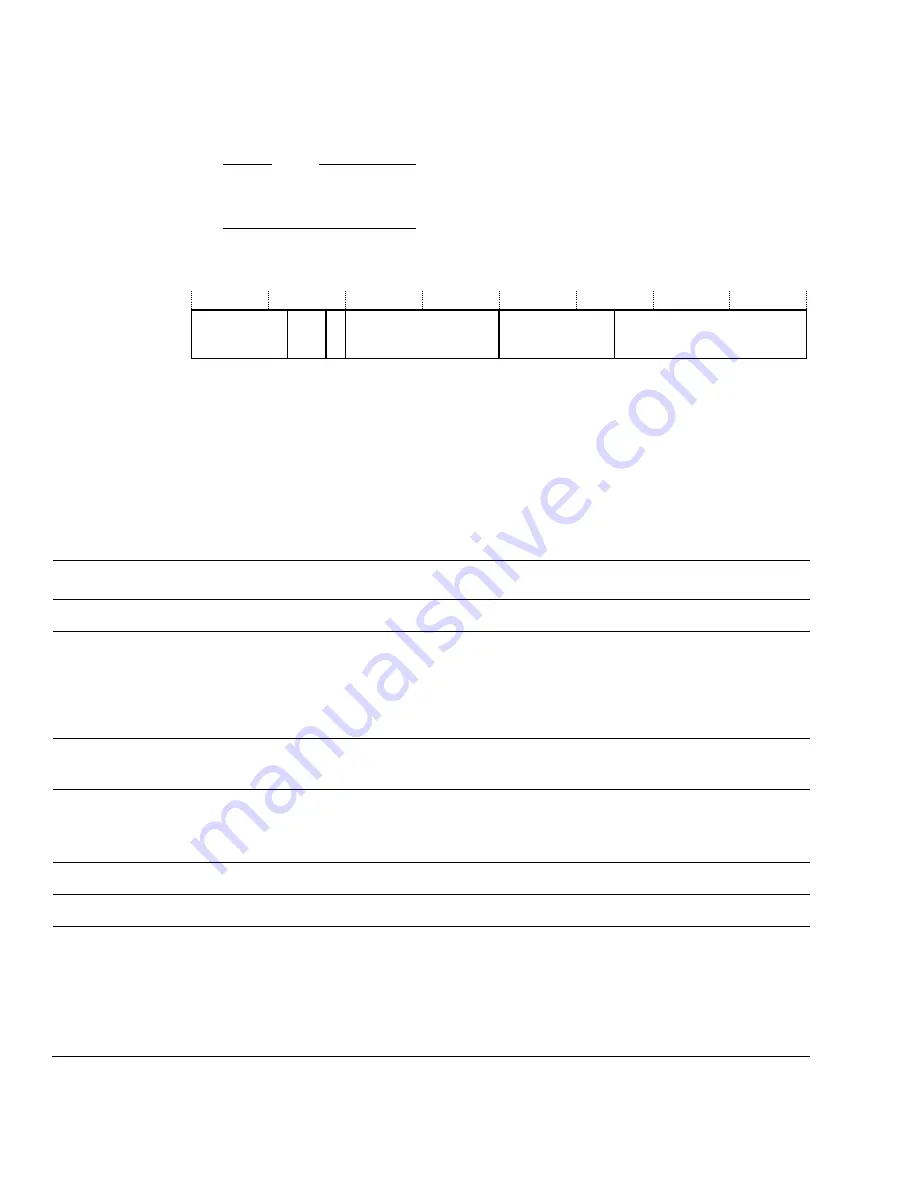

Figure 2-4 shows the bit assignments of the EPSR.

Figure 2-4 Execution Program Status Register

The EPSR is not directly accessible. Two events can modify the EPSR:

•

an interrupt occurring during an LDM or STM instruction

•

execution of the If-Then instruction.

Table 2-3 describes the bit assignments of the EPSR.

31

0

Reserved

Reserved

27 26 25 24

16 15

10 9

Reserved

ICI/IT

ICI/IT

23

T

Table 2-3 Bit functions of the EPSR

Field Name

Definition

[31:27]

- Reserved.

[26:25], [15:10]

ICI

Interruptible-continuable instruction bits. When an interrupt occurs during an LDM or STM

operation, the multiple operation stops temporarily. The EPSR uses bits [15:12] to store the

number of the next register operand in the multiple operation. After servicing the interrupt,

the processor returns to the register pointed to by [15:12] and resumes the multiple

operation.

[26:25], [15:10]

IT

If-Then bits. These are the execution state bits of the If-Then instruction. They contain the

number of instructions in the if-then block and the conditions for their execution.

[24]

T

The T-bit can be cleared using an interworking instruction where bit [0] of the written PC

is 0. It can also be cleared by unstacking from an exception where the stacked T bit is 0.

Executing an instruction while the T bit is clear causes an INVSTATE exception.

[23:16]

- Reserved.

[9:0]

- Reserved.